# TISSU NUMÉRIQUE CELLULAIRE À ROUTAGE ET CONFIGURATION DYNAMIQUES

### THÈSE N° 3226 (2005)

#### PRÉSENTÉE À LA FACULTÉ INFORMATIQUE ET COMMUNICATIONS

Institut des systèmes informatiques et multimédias

SECTION D'INFORMATIQUE

#### ÉCOLE POLYTECHNIQUE FÉDÉRALE DE LAUSANNE

POUR L'OBTENTION DU GRADE DE DOCTEUR ÈS SCIENCES

#### **PAR**

### Yann THOMA

ingénieur informaticien diplômé EPF de nationalité suisse et originaire d'Amden (SG)

acceptée sur proposition du jury:

Prof. E. Sanchez, directeur de thèse Prof. G. De Micheli, rapporteur Prof. D. Lavenier, rapporteur Dr G. Sassatelli, rapporteur

# Version abrégée

A l'instar des premiers concepteurs d'avions, l'homme a toujours observé la nature, qui lui a fourni des pistes lors de la création de nouvelles machines ou de nouveaux concepts. Les circuits électroniques ne font pas exception, et les trois axes de la vie que sont l'évolution des espèces (Phylogenèse), le développement de l'organisme à partir d'une seule cellule (Ontogenèse), ainsi que l'apprentissage dont notre cerveau est capable (Epigenèse), ont vu nombre de réalisations s'en inspirer.

Ces trois axes, qui forment l'acronyme POE, ont été, pour la plupart des réalisations, exploités séparément : les principes de l'évolution permettent de résoudre des problèmes pour lesquels il est difficile d'obtenir une solution de façon déterministe, des circuits électroniques tirent profit des concepts d'autoréparation du vivant, et les réseaux de neurones artificiels sont capables d'effectuer efficacement un grand nombre de tâches. Leur réunion en un seul *tissu* électronique n'a en revanche pas encore vu le jour.

Concernant la réalisation matérielle de tels systèmes, l'avènement des circuits reconfigurables FPGAs, dont il est possible de redéfinir un nombre quasi infini de fois le comportement, en a facilité le prototypage. Ils permettent en effet d'accélérer l'exécution d'une tâche, par le parallélisme matériel qu'ils offrent, et ont été grandement exploités par les chercheurs. Toutefois, ils manquent de plasticité, leur comportement ne pouvant facilement se modifier lui-même sans une intervention extérieure.

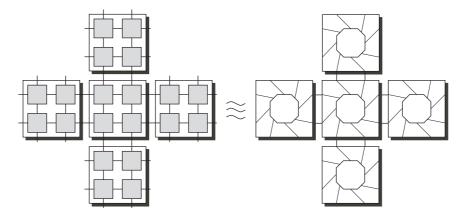

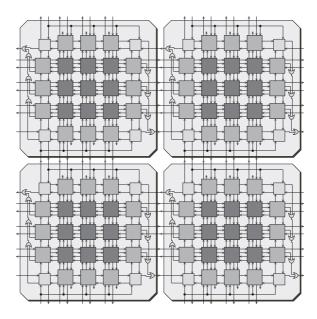

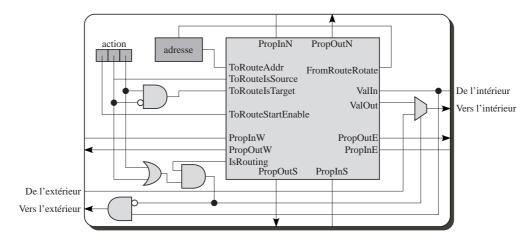

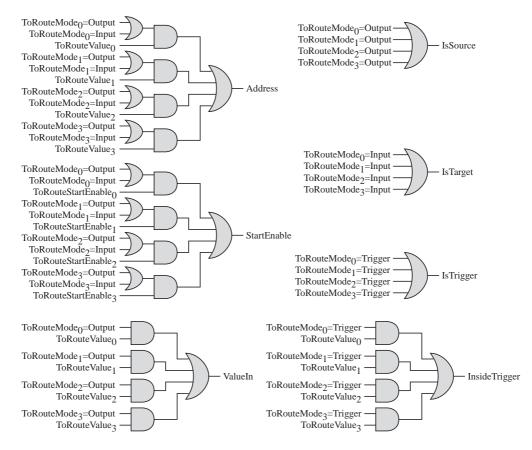

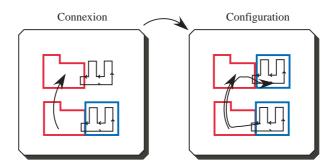

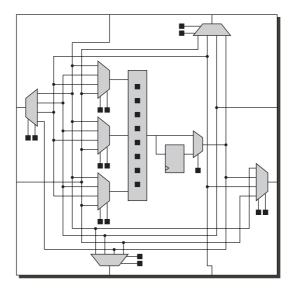

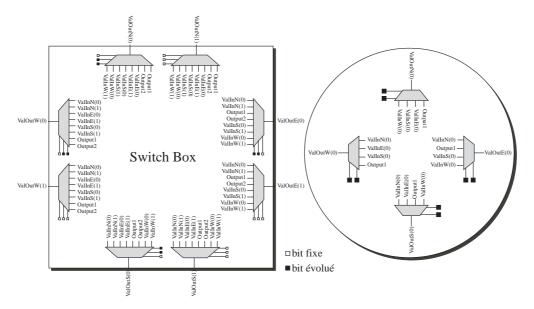

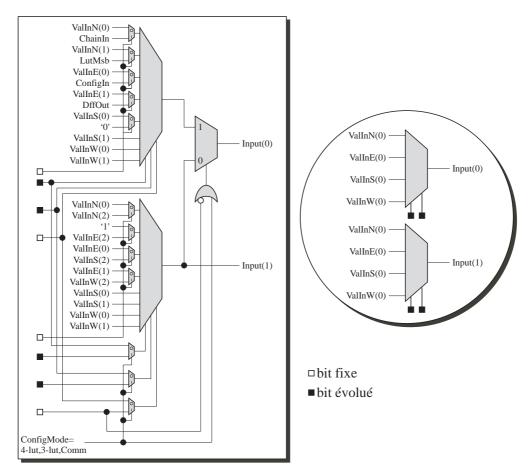

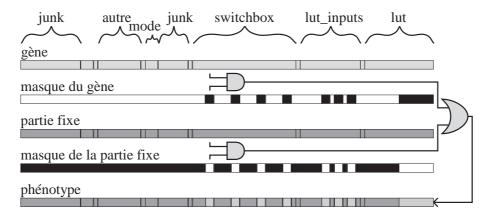

Cette thèse, qui s'insère dans le cadre du projet européen POEtic, se propose de définir un nouveau circuit électronique reconfigurable, dans l'optique de fournir un nouveau substrat aux applications bio-inspirées mettant en jeu ces trois axes. Ce circuit est composé d'un microprocesseur, et d'un tableau d'éléments reconfigurables, ce dernier ayant été réalisé par nos soins. Les processus évolutifs sont exécutés par le premier, alors que l'épigenèse et l'ontogenèse prennent place dans le deuxième, sous la forme d'organismes artificiels multicellulaires. Relativement semblable aux FPGAs commerciaux actuels, ce sous-système offre cependant de nouvelles caractéristiques intéressantes. Premièrement, les éléments de base du tableau ont la capacité de reconfigurer partiellement d'autres éléments. Des mécanismes d'auto-réplication et de différenciation peuvent alors l'exploiter pour laisser un organisme artificiel croître ou modifier son comportement. Deuxièmement, un niveau de routage distribué offre la possibilité de créer des connexions entre différentes parties du circuit pendant son fonctionnement. Les cellules qui y sont implémentées, notamment les neurones artificiels, peuvent alors initier de nouvelles connexions, de manière à modifier le comportement global du système.

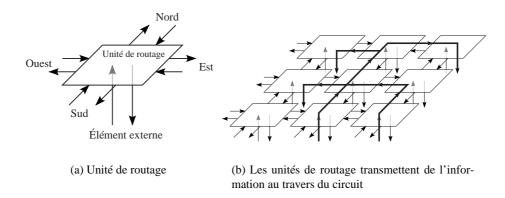

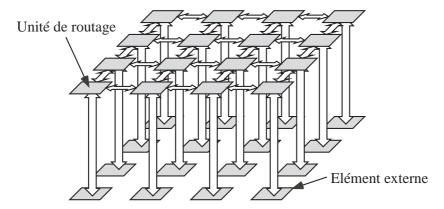

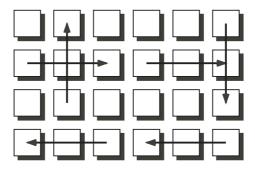

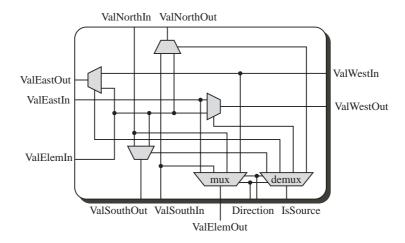

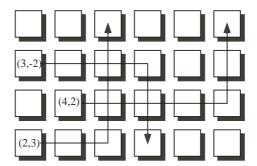

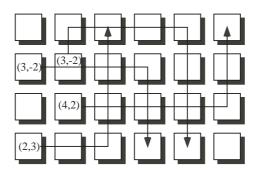

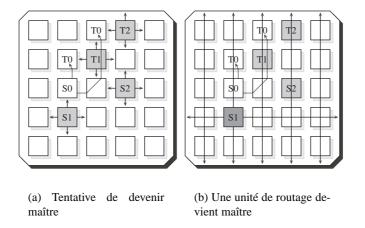

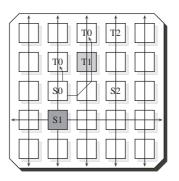

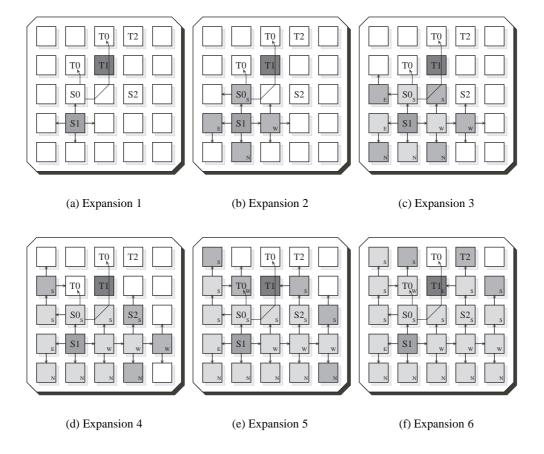

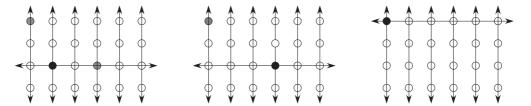

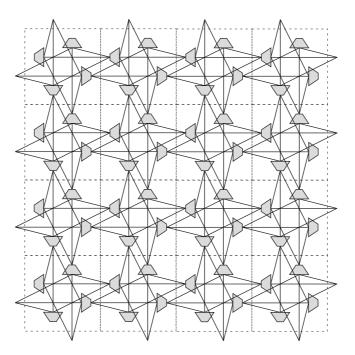

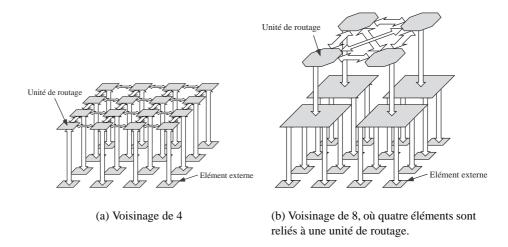

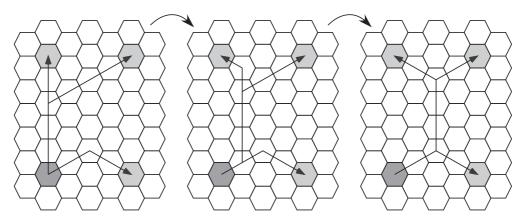

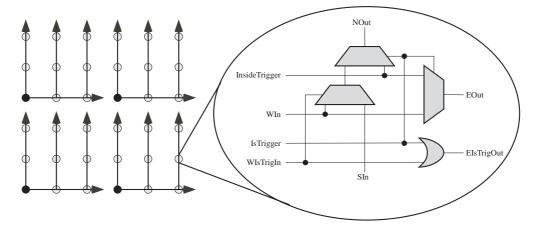

Ce routage distribué, qui constitue l'un des points importants de cette thèse, a vu la réalisation de plusieurs algorithmes. Basés sur une implémentation parallèle de l'algorithme de Lee, ils sont totalement distribués, c'est-à-dire qu'aucun contrôle global n'est nécessaire à la création de chemins de données. Quatre algorithmes sont ainsi définis et décrits matériellement sous la forme d'unités de routage reliées à leurs 3, 4, 6, ou 8 voisines, toutes identiques, qui gèrent les processus de routage. Une analyse de leurs propriétés nous permet de définir le meilleur algorithme à coupler au plus efficace des voisinages, en terme de congestion, par rapport au nombre de tran-

sistors nécessaires à leur réalisation. Nous terminons sur le routage en proposant un cinquième algorithme, qui, contrairement aux quatre précédents, n'est construit que sur des communications locales entre unités de routage. Il offre ainsi, au prix d'un coût matériel supplémentaire, une meilleure scalabilité au système complet.

Finalement, le circuit POEtic, sur lequel un de nos algorithmes de routage a été implémenté, a été physiquement réalisé. Nous présentons différents mécanismes POE qui tirent profit de ses caractéristiques nouvelles et qui peuvent y être embarqués. Parmi ces mécanismes, nous pouvons citer notamment l'auto-réplication, le matériel évolutif, les systèmes développementaux, et l'autoréparation, qui ont été développés grâce à un simulateur du circuit, également conçu durant cette thèse.

## **Abstract**

In the design of new machines or in the development of new concepts, mankind has often observed nature, looking for useful ideas and sources of inspiration. The design of electronic circuits is no exception, and a considerable number of realizations have drawn inspiration from three aspects of natural systems: the evolution of species (Phylogenesis), the development of an organism starting from a single cell (Ontogenesis), and learning, as performed by our brain (Epigenesis).

These three axes, grouped under the acronym POE, have for the most part been exploited separately: evolutionary principles allow to solve problems for which it is hard to find a solution with a deterministic method, while some electronic circuits draw inspiration from healing process in living beings to achieve self-repair, and artificial neural networks have the capability to efficiently execute a wide range of tasks. At this time, no electronic *tissue* capable of bringing them together seems to exist.

The introduction of reconfigurable circuits called Field Programmable Gate Arrays (FPGAs), whose behavior can be redefined as often as desired, made prototyping such systems easier. FPGAs, by allowing a relatively simple implementation in hardware, can considerably increase the systems' performance and are thus extensively used by researchers. However, they lack plasticity, not being able to easily modify themselves without an external intervention.

This PhD thesis, developed in the framework of the European POEtic project, proposes to define a new reconfigurable electronic circuit, with the goal of supplying a new substrate for bio-inspired applications that bring all three axes into play. This circuit is mainly composed of a microprocessor and an array of reconfigurable elements, the latter having been designed during this thesis. Evolutionary processes are executed by the microprocessor, while epigenetic and ontogenetic mechanisms are applied in the reconfigurable array, to entities seen as multicellular artificial organisms. Relatively similar to current commercial FPGAs, this subsystem offers however some unique features. First, the basic elements of the array have the capability to partially reconfigure other elements. Auto-replication and differentiation mechanisms can exploit this capability to let an organism grow or to modify its behavior. Second, a distributed routing layer allows to dynamically create connections between parts of the circuit at runtime. With this feature, cells (artificial neurons, for example) implemented in the reconfigurable array can initiate new connections in order to modify the global system behavior.

This distributed routing mechanism, one of the major contributions of this thesis, induced the realization of several algorithms. Based on a parallel implementation of Lee's algorithm, these algorithms are totally distributed, no global control being necessary to create new data paths. Four algorithms have been defined implemented in hardware in the form of routing units connected to 3, 4, 6, or 8 neighbors. These units are all identical and are responsible for the routing processes. An analysis of their properties allows us to define the best algorithm, coupled with the most efficient neighborhood, in terms of congestion and of the number of transistors needed for a hardware realization. We finish the routing chapter by proposing a fifth algorithm that, unlike the previous ones, is constructed only through local interactions between routing units. It

offers a better scalability, at the price of increased hardware overhead.

Finally, the POEtic chip, in which one of our algorithms has been implemented, has been physically realized. We present different POE mechanisms that take advantage of its new features. Among these mechanisms, we can notably cite auto-replication, evolvable hardware, developmental systems, and self-repair. All of these mechanisms have been developed with the help of a circuit simulator, also designed in the framework of this thesis.

## Remerciements

La vie, c'est comme une bicyclette, il faut avancer pour ne pas perdre l'équilibre.

Albert EINSTEIN

Ah, les remerciements. Derniers mots posés, qui ne sont de loin pas les plus évidents, la mémoire étant un système très efficace, mais pas entièrement fiable. Je vais toutefois essayer d'éviter d'omettre les acteurs les plus importants, en m'excusant déjà auprès des pauvres oubliés qui peuvent toutefois être sûrs que leur présence a été également appréciée.

Cette thèse n'aurait pas vu le jour sans l'existence du Laboratoire de Systèmes Logiques (LSL), dirigé de main de maître par Daniel Mange. Sans lui mon destin aurait possiblement été fort différent, puisque les recherches du laboratoire dans le domaine de la bio-inspiration ont pesés dans la balance me faisant choisir l'EPFL plutôt que l'Université de Genève comme lieu d'études. Ayant abandonné l'idée de devenir éthologue, mêler les principes du vivant aux outils informatiques m'a semblé la voie à suivre. Merci donc à Daniel, pour m'avoir si chaleureusement accueilli dans son laboratoire, et pour ses qualités oratoires qui resteront pour moi un modèle à suivre.

Que serait une thèse sans directeur de thèse? Bien peu de chose, assurément. Eduardo DJ Sanchez, qui m'a donné le goût des systèmes logiques lors de ma première année d'études EPFLiennes, s'est trouvé tout naturellement à cette place cruciale en me proposant de travailler sur le projet POEtic. La liberté qu'il m'a (trop?) laissée m'a permis d'aiguiser mes armes scientifiques et critiques, et de mener à bien ce travail. Bien plus qu'un directeur, Eduardo restera un ami dont la culture musicale et la collection de CDs me feront toujours pâlir de jalousie, et dont j'espère pouvoir encore goûter les côtelettes grillées dont il a le secret.

Outre ses deux figures charismatiques, orateurs hors pairs, dont la rigueur du premier et l'accent du deuxième sont l'essence même du LSL, une foule de personnalités constituent le liant de ce laboratoire à l'ambiance exceptionnelle. Commençons par mes collègues de bureau. Le premier à avoir quitté la salle magique INN235 est Mathieu key-destroyer, la terreur des claviers, dont j'attends avec impatience le retour en terre vaudoise. Ce fut ensuite Professeur Gianluca qui le suivit, emportant avec lui sa musique, sujet sur lequel nos accords avaient, il faut l'avouer, une fâcheuse tendance à sonner faux. Enrico, troisième sur la liste et guitariste émérite nous a, quant à lui, laissé en héritage son tube planétaire F... Sunshine, que j'ai encore plaisir à écouter. Enfin, remplaçant les départs, Fabien l'homme de l'air prit la place de Mathieu. Toujours prêt à décoller, autant en journée qu'en soirée, j'ai eu fort plaisir à nos collaborations Biowalliennes. Enfin, dernier arrivé, Ludovic, le plus dark des metal allemands a su imposer un ton musical hors norme qui ne fut pas pour me déplaire.

Séparés par quelques murs, nous retrouvons Alessandro, l'homme dont le clavier tape plus vite que son ombre et qui est capable de résoudre le plus obscur des soucis informatiques. Dans le même bureau, Jonas est l'homme qui me fit découvrir la

percolation. Je le remercie infiniment pour ses suggestions mathématiques toujours judicieuses. Andres, le dernier des Colombiens (hormis notre bien-aimé Eduardo), bien qu'ayant mis du temps à nous rejoindre aux pauses de midi, a bien fait de s'y mettre, sa bonne humeur éternelle étant plus qu'appréciable. Dernier habitant de ce bureau, Yvan y est arrivé pour renforcer encore notre présence à la cafétéria du DMX, haut lieu culinaire du site de l'EPFL, que Marie-Thérèse gère de la plus belle des manières. De l'autre côté du couloir, nous trouvons Pierre-André et Joël. Tous deux ont su amener un souffle nouveau, et une excellente ambiance au renouveau des fameuses soirées bières.

N'oublions pas les anciens doctorants. Christof, tout d'abord, modèle de travailleur acharné, qui rendrait modeste le plus bosseur d'entre nous. Grâce à lui je suis toujours au faîte de l'actualité de la mode vestimentaire de l'Association des Super Suisses. Ralph ensuite, toujours discret et rigoureux, dont l'efficacité au laser-game est impressionnante. Les valaisans Jaco et Jean-Luc, dont le premier est la seule personne que je connaisse capable de fumer un bouchon, et dont le deuxième, sous des apparence débonnaires écoute une musique des plus sauvages, ont amené au labo des breuvages douteux et goûteux qui ont agrémentés nos soirées folles. Et du côté colombien, Carlos Andrés et Fabio, dont j'apprécie particulièrement le calme et la sérénité, sont deux papas qui ont des enfants plus que chanceux.

Le laboratoire ne serait rien sans Marlyse, notre secrétaire, qui illumine ce laboratoire de son sourire radieux et de sa bonne humeur, et qui fut agréablement secondée par Natascha. Leur gentillesse, de même que leur promptitude à résoudre le moindre souci administratif, sont définitivement un des atouts du LSL. Et n'oublions pas André Chico Jeux-de-maux Badertscher, toujours à l'affût de la donzelle passant dans nos couloirs, et à qui je dois un petit coup de pouce du destin. Au bout de ce même couloir, nous trouvons Auke, professeur qui a insufflé encore plus de bio-inspiration aux recherches du LSL, tout en y amenant un niveau d'ondes positives très apprécié. Terminons ce survol par deux figures légendaires, JK et André Stauffer. JK, expert logicien, m'a fait passer l'oral le plus rapide de mon existence durant mes études à l'EPFL (avec fin heureuse, je vous rassure), et s'est mué collègue à l'humour toujours à la pointe du bon ton. André, quant à lui, est l'homme graphique du LSL, et son écriture manuscrite continue encore à m'impressionner.

Merci à tous pour ces quatre années radieuses. En sortant des études d'ingénieur je pensais savoir beaucoup de choses, et la confrontation à tant de matière grise et de générosité m'a définitivement appris l'humilité.

Je remercie vivement mes relecteurs occasionnels, Fabien, Joël et Eduardo, qui ont insufflé un peu plus de clarté dans ce document, et Gianluca pour les corrections anglaises. Une mention spéciale va au professeur Langaney, dont j'ai toujours autant de plaisir à écouter les exposés sur l'évolution des espèces, et qui a bien voulu partir à l'assaut des erreurs du troisième chapitre. Merci également à Marc pour nos quelques échanges fructueux, et à Marcel pour les discussions statistiques que nous avons eues.

Et n'oublions pas les rapporteurs qui ont lu et approuvé ce travail : le professeur Dominique Lavenier, le professeur Giovanni de Micheli, et le docteur Gilles Sassatelli, de même que le directeur du jury, le professeur Paolo Ienne.

Mes remerciements vont également aux membres du projet POEtic, avec qui j'ai eu beaucoup de plaisir à collaborer et à festoyer à Barcelone, York, Glasgow, et Lausanne. Je pense y avoir entre autre appris qu'il n'est pas des plus évident de coordonner une équipe répartie aux quatre coins de l'Europe. Heureusement que Daniel Roggen

travaillait sur le site de l'EPFL, nous avons ainsi pu partager nos doutes et espoirs durant les trois ans que dura le projet.

Quittons à présent le monde du travail, pour nous approcher des personnes à qui je dois mon équilibre. Mes remerciements les plus chaleureux vont aux membres de ma famille, qui m'ont permis d'effectuer mes études à l'EPFL, et ont toujours su être présents, malgré ma fâcheuse tendance à passer un temps plus que certain hors du logis familial.

Un esprit sain dans un corps sain? Alors que je tentais d'affûter le premier au laboratoire, le basket-ball m'a apporté un équilibre nécessaire au bon fonctionnement de mon organisme. Mes partenaires du Vermont Basket II y sont pour beaucoup, de même que les joueurs occasionnels avec qui j'ai toujours autant de plaisir à tapoter le ballon orange.

Le sport, ainsi qu'une certaine forme de raisonnement sont, à mon avis, indispensables à l'équilibre du corps. La situation se complique un peu lorsque la musique occupe une place également importante. J'ai tenté tant bien que mal de partager ma vie entre le laboratoire, le basketball, les répétitions, et les relations humaines (sans que cet ordre ne signifie une quelconque préférence, rassurez-vous). Les musiciens des Braibs et d'Exunda ont dès lors tenu une place importante dans mon équilibre, et je les remercie infiniment pour les moments musicaux que nous avons partagés.

Je tiens également à remercier ici Inès pour son soutien lors des doutes de début de thèse, alors que la direction de mes recherches tentait de se définir. Et évidemment, mes amis de toujours, Marcel, Joël et Christophe, avec qui j'ai toujours autant de plaisir à partir à la conquête du Sud de la France. Le mélange économètre-éducateur-sociologue-informaticien nous offre de forts beaux débats, auxquels j'espère pouvoir participer encore longtemps. Merci donc à vous d'être vous. Ne changez rien.

Finalement, un merci particulier à Stéphanie, qui a eu la lourde tâche de me soutenir durant les deux dernières années de mon travail. Sa patience et ses encouragements m'ont largement aidé à mener à bien cette thèse.

# Table des matières

| Ve | ersion | abrégée                                    | i    |

|----|--------|--------------------------------------------|------|

| Al | bstrac | et                                         | iii  |

| R  | emerc  | iements                                    | v    |

| Ta | ble d  | es matières                                | viii |

| 1  | Prol   | égomènes                                   | 1    |

|    | 1.1    | Réflexions pré-introductives               | 1    |

|    | 1.2    | Motivations POEtiques                      | 2    |

|    | 1.3    | Contributions                              | 4    |

|    | 1.4    | Contenu de la thèse                        | 5    |

| 2  | De l   | a configuration des circuits électroniques | 7    |

|    | 2.1    | Processeur                                 | 8    |

|    | 2.2    | ASIC                                       | 9    |

|    |        | 2.2.1 A la demande                         | 9    |

|    |        | 2.2.2 Prédiffusés                          | 9    |

|    |        | 2.2.3 Pré-caractérisés                     | 11   |

|    |        | 2.2.4 A réseau structuré                   | 11   |

|    |        | 2.2.5 Limitations                          | 12   |

|    | 2.3    | Technologies de programmation              | 12   |

|    |        | 2.3.1 Masque                               | 12   |

|    |        | 2.3.2 Fusible                              | 13   |

|    |        | 2.3.3 Antifusible                          | 13   |

|    |        | 2.3.4 EPROM                                | 14   |

|    |        | 2.3.5 EEPROM/Flash                         | 15   |

|    |        | 2.3.6 SRAM                                 | 15   |

|    |        | 2.3.7 Résumé                               | 16   |

|    | 2.4    | Circuits logiques programmables            | 17   |

|    |        | 2.4.1 SPLD                                 | 17   |

|    |        | 2.4.2 CPLD                                 | 19   |

|    | 2.5    | FPIC                                       | 20   |

|    | 2.6    | FPGAs                                      | 20   |

|   |      | 2.6.1    | XC2000                        | 21 |

|---|------|----------|-------------------------------|----|

|   |      | 2.6.2    | XC6200                        | 23 |

|   |      | 2.6.3    | Architecture MUX versus LUT   | 24 |

|   |      | 2.6.4    | Technologies de programmation | 25 |

|   |      | 2.6.5    | Accroissement de complexité   | 26 |

|   |      | 2.6.6    | Fabricants                    | 28 |

|   |      | 2.6.7    | Placement/Routage             | 32 |

|   |      | 2.6.8    | FPGA versus ASIC              | 32 |

|   | 2.7  |          | usion                         | 33 |

| 3 | De l | a bio-in | spiration                     | 35 |

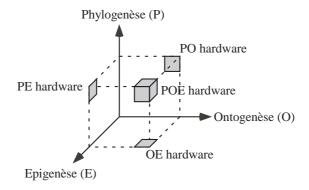

|   | 3.1  | Le mo    | dèle POE                      | 36 |

|   | 3.2  | La vie   | en 3 axes                     | 37 |

|   |      | 3.2.1    | Phylogenèse                   | 37 |

|   |      | 3.2.2    | Ontogenèse                    | 42 |

|   |      | 3.2.3    | Epigenèse                     | 44 |

|   | 3.3  | Les Sy   | vstèmes artificiels en 3 axes | 45 |

|   |      | 3.3.1    | Phylogenèse                   | 45 |

|   |      | 3.3.2    | Ontogenèse                    | 51 |

|   |      | 3.3.3    | Epigenèse                     | 53 |

|   | 3.4  | Combi    | inaisons                      | 60 |

|   |      | 3.4.1    | PO                            | 60 |

|   |      | 3.4.2    | PE                            | 61 |

|   |      | 3.4.3    | OE                            | 62 |

|   |      | 3.4.4    | POE                           | 62 |

|   | 3.5  | Le pro   | jet POEtic                    | 62 |

|   |      | 3.5.1    | Nomenclature                  | 63 |

|   |      | 3.5.2    | Architecture POEtic           | 63 |

|   |      | 3.5.3    | Pourquoi un nouveau circuit ? | 65 |

| 4 | Le r | outage   | au fil des ans                | 67 |

|   | 4.1  | Pourqu   | uoi un plus court chemin?     | 67 |

|   | 4.2  | Aparté   | Enaturel                      | 68 |

|   |      | 4.2.1    | Les fourmis                   | 68 |

|   |      | 4.2.2    | Les bulles de savon           | 69 |

|   |      | 4.2.3    | Le gaz, le son, la lumière    | 70 |

|   |      | 4.2.4    | De la ficelle                 | 70 |

|   | 4.3  | Les Ba   | ases théoriques               | 71 |

|   |      | 4.3.1    | Arbre de poids minimal        | 71 |

|   |      | 4.3.2    | Plus court chemin             | 73 |

|   |      | 4.3.3    | Algorithme de Lee             | 78 |

|   |      | 4.3.4    | Variations sur Lee            | 81 |

|   |      | 4.3.5    | A* et algorithmes évolués     | 87 |

|   | 4.4  | Appro    | ches Matérielles              | 88 |

|   |      | 4.4.1    | Routage de FPGA               | 89 |

|   |      | 4.4.2    | Coprocesseur                  | 89 |

|   |      | 4.4.3    | Processeur                    | 90 |

|   |      | 111      | CIMD                          | OΛ |

|   |      | 4.4.5     | MIMD                                                | 90    |

|---|------|-----------|-----------------------------------------------------|-------|

|   |      | 4.4.6     | Analogique                                          | 90    |

|   |      | 4.4.7     | Tableau de cellules pour la réalisation de circuits | . 91  |

|   |      | 4.4.8     | Tableau de cellules pour du matériel bio-inspiré    | . 94  |

|   | 4.5  | Conclu    |                                                     |       |

| 5 | Ler  | nutage d  | distribué                                           | 97    |

| ٠ | 5.1  | _         | ot                                                  |       |

|   | 5.2  | _         | es                                                  |       |

|   | 5.3  | -         | nèses                                               |       |

|   | 5.4  | • •       | res solutions                                       |       |

|   | 0    | 5.4.1     | Algorithme direct                                   |       |

|   |      | 5.4.2     | Algorithme à adressage relatif direct               |       |

|   |      | 5.4.3     | Algorithme à adressage relatif indirect             |       |

|   | 5.5  |           |                                                     |       |

|   | 3.3  | 5.5.1     | Algorithme                                          |       |

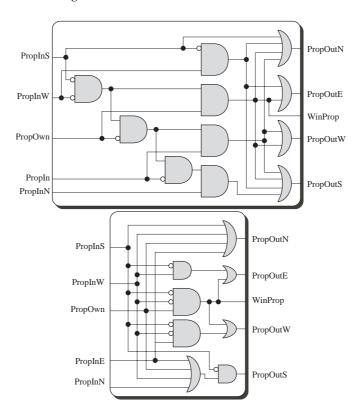

|   |      | 5.5.2     | Unité de routage                                    |       |

|   | 5.6  |           | A-RC                                                | -     |

|   | 5.7  |           | A-RT                                                |       |

|   | 5.8  |           | A-RTC                                               |       |

|   | 5.9  |           | A-L                                                 |       |

|   | 3.7  | 5.9.1     | Algorithme                                          |       |

|   |      | 5.9.2     | Implémentation                                      |       |

|   | 5 10 |           | ages                                                |       |

|   | 3.10 |           | Switchboxs                                          |       |

|   |      |           | Nombre total de transistors                         |       |

|   |      |           | 4 versus 8                                          |       |

|   | 5 11 |           | e                                                   |       |

|   | 3.11 | -         | Expérience                                          |       |

|   |      |           | Temps d'exécution                                   | _     |

|   |      |           | Longueur de chemins                                 |       |

|   |      |           | Nombre de multiplexeurs                             |       |

|   |      |           |                                                     | 156   |

|   |      |           | Congestion                                          |       |

|   | 5 12 |           |                                                     |       |

|   | 3.12 | Concia    |                                                     | 107   |

| 6 | Le C | Circuit P |                                                     | 171   |

|   | 6.1  | Structu   | re globale                                          | 173   |

|   | 6.2  |           | s-système organique                                 |       |

|   | 6.3  | Les Mo    | plécules                                            |       |

|   |      | 6.3.1     | Mode 4-LUT                                          | 177   |

|   |      | 6.3.2     | Mode 3-LUT                                          | 178   |

|   |      | 6.3.3     | Mode Comm                                           | 178   |

|   |      | 6.3.4     | Mode Shift Memory                                   | . 179 |

|   |      | 6.3.5     | Mode Input                                          | 180   |

|   |      | 6.3.6     | Mode Output                                         | 181   |

|   |      | 6.3.7     | Mode Trigger                                        | 182   |

|   |      | 6.3.8     | Mode Configure                                      |       |

|   |      | 6.3.9   | Entrées/sorties                                    | 184 |

|---|------|---------|----------------------------------------------------|-----|

|   |      | 6.3.10  | Communication intermoléculaire                     | 187 |

|   |      | 6.3.11  | Multiplexeurs d'entrée                             | 190 |

|   |      | 6.3.12  | Bits de configuration et reconfiguration partielle | 192 |

|   |      | 6.3.13  | Enable moléculaire                                 | 195 |

|   |      | 6.3.14  | Gestion de la bascule                              | 196 |

|   |      |         | Look-up table                                      | 198 |

|   | 6.4  |         | age distribué                                      | 198 |

|   |      | 6.4.1   | Routage pseudo-statique                            | 199 |

|   |      | 6.4.2   | Entrées/sorties et systèmes multi-chip             | 200 |

|   |      | 6.4.3   | Interface molécule/unité de routage                | 202 |

|   | 6.5  | Le sous | s-système environnemental                          | 203 |

|   | 6.6  |         | face du système                                    | 206 |

|   | 6.7  |         | ution du circuit                                   | 207 |

|   | 6.8  |         | nentation de composants de base                    | 208 |

|   |      | 6.8.1   | Le registre à décalage                             | 208 |

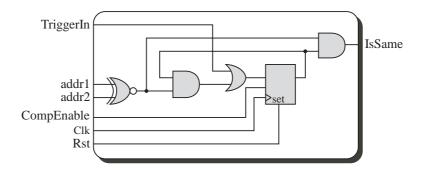

|   |      | 6.8.2   | Le compteur                                        | 211 |

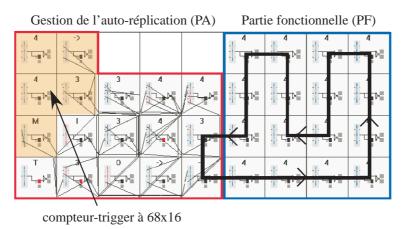

|   |      | 6.8.3   | Le compteur-trigger                                | 211 |

|   | 6.9  |         | tils de développement                              | 215 |

|   | 0.7  | 6.9.1   | Design                                             | 215 |

|   |      | 6.9.2   | Simulation                                         | 216 |

|   | 6.10 | Conclu  |                                                    | 218 |

|   | 0.10 |         | Comparaison                                        | 218 |

|   |      |         | Améliorations                                      | 219 |

|   |      |         |                                                    |     |

| 7 | Méca | anismes | POE                                                | 221 |

|   | 7.1  | Autoré  | plication                                          | 222 |

|   | 7.2  | Dévelo  | ppement                                            | 224 |

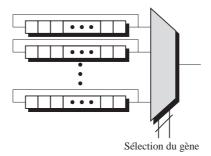

|   |      | 7.2.1   | Stockage de génome                                 | 225 |

|   |      | 7.2.2   | Croissance                                         | 226 |

|   |      | 7.2.3   | Différenciation                                    | 230 |

|   | 7.3  | Un exe  | mple concret: le prototype PO                      | 230 |

|   |      | 7.3.1   | Implémentation physique                            | 231 |

|   |      | 7.3.2   | Structure cellulaire                               | 231 |

|   |      | 7.3.3   | Mécanisme de développement                         | 232 |

|   |      | 7.3.4   | Evolution                                          | 234 |

|   |      | 7.3.5   | Remarques conclusives                              | 236 |

|   | 7.4  | Matérie | el évolutif non-contraint                          | 236 |

|   |      | 7.4.1   | La look-up table                                   | 238 |

|   |      | 7.4.2   | Le switchbox                                       | 238 |

|   |      | 7.4.3   | Les entrées                                        | 239 |

|   |      | 7.4.4   | Représentation du génome                           | 239 |

|   |      | 7.4.5   | Caractéristiques de l'évolution                    | 242 |

|   | 7.5  | Autres  | exemples                                           | 242 |

|   |      | 7.5.1   | Autoréparation                                     | 242 |

|   |      | 7.5.2   | Synthèse vocale                                    | 243 |

|   |      | 7.5.3   | Neurone à impulsion                                | 244 |

|   |      |         |                                                    |     |

TABLE DES MATIÈRES

|   | ٠ | ٠ | ٠ |  |

|---|---|---|---|--|

| Y | 1 | 1 | 1 |  |

| 8   | Con    | clusions              | 245 |

|-----|--------|-----------------------|-----|

|     | 8.1    | Le routage distribué  | 245 |

|     | 8.2    | Conclusions POEtiques | 247 |

| Lis | ste de | es Figures            | 251 |

| Lis | ste de | es Tableaux           | 257 |

| Lis | ste de | es Algorithmes        | 259 |

| Bil | oliog  | raphie                | 261 |

| Cu  | rricu  | ılum vitæ             | 279 |

# Prolégomènes

Entre

Ce que je pense,

Ce que je veux dire,

Ce que je crois dire,

Ce que je dis,

Ce que vous avez envie d'entendre,

Ce que vous croyez entendre,

Ce que vous entendez,

Ce que vous avez envie de comprendre,

Ce que vous comprenez,

Il y a dix possibilités qu'on ait des difficultés à communiquer.

Mais essayons quand même...

Bernard WERBER, Le père de nos pères

### 1.1 Réflexions pré-introductives

De tout temps l'homme s'est inspiré de la nature pour construire des machines, à la manière dont les oiseaux motivèrent les pionniers de la conquête des airs. Sur le plan des technologies de l'information, bien que les travaux de von Neumann sur les architectures des premiers processeurs visaient à créer un système capable d'imiter le comportement du cerveau, cette bio-inspiration n'y est que peu présente. Les microprocesseurs, qui sont aussi bien exploités par les ordinateurs et par les téléphones mobiles que par les machines à laver, n'embarquent pas de mécanismes semblables à ceux observés dans la nature.

Cependant, les systèmes aussi bien matériels que logiciels faisant intervenir des processus inspirés du vivant sont de plus en plus nombreux. A titre d'exemples, citons les réseaux de neurones artificiels qui analysent les adresses écrites à la main sur les lettres envoyées par la Poste, et la main artificielle de l'équipe d'Higuchi [116] qui s'adapte à son hôte : ces deux exemples ne sont qu'une infime partie de la recherche effectuée dans le domaine des systèmes bio-inspirés.

Mais pourquoi vouloir à tout prix s'inspirer du vivant ? Tout simplement parce que la vie est impressionnante de plasticité et d'adaptabilité. Depuis son apparition, il y a quelques milliards d'années, elle n'a cessé de se complexifier, jusqu'aux organismes que nous connaissons actuellement, en inventant sans cesse de nouvelles stratégies et de nouveaux systèmes. De plus, les capacités d'autoréparation du vivant sont impressionnantes. Alors qu'un ordinateur "plante" lamentablement si un seul des innombrables signaux qui le composent change subrepticement d'état, les organismes vivants peuvent survivre à des blessures ou aux maladies. Enfin, les capacités d'apprentissage des êtres dits supérieurs sont surprenantes, tandis que les machines peinent encore à tirer parti des expériences vécues, et à les généraliser.

#### 1.2 Motivations POEtiques

Dans cette thèse, nous nous intéresserons particulièrement au modèle POE, qui vise à décrire les systèmes matériels bio-inspirés selon trois axes : Phylogénétique, relatif à l'évolution, Ontogénétique, pour ce qui est de la croissance et de l'autoréparation, et Épigénétique, en ce qui concerne l'apprentissage. Différentes applications peuvent mettre en oeuvre un, deux ou trois de ces axes, en fonction du problème à résoudre.

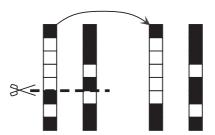

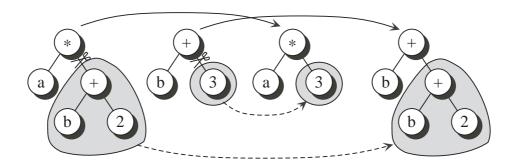

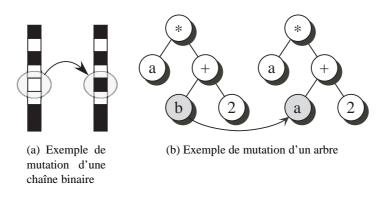

La phylogenèse traite, sur le plan du vivant, de l'évolution des espèces, et de la manière dont les gènes sont transmis des parents à la progéniture. Diverses théories coexistent, allant du néo-darwinisme au Lamarckisme, en passant par celle des équilibres ponctués et celle des monstres prometteurs. Elles ont inspiré des chercheurs qui en ont tiré le concept d'algorithme génétique, visant à résoudre un problème complexe pour lequel la solution ne peut être trouvée en un temps raisonnable par un algorithme déterministe. Le concept y est le suivant : une population d'individus représentés chacun par un génome est générée aléatoirement et les individus sont évalués puis sélectionnés selon un critère particulier au type de problème. La nouvelle population est alors réévaluée, et le cycle recommence jusqu'à approcher une solution acceptable.

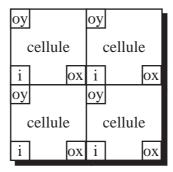

L'ontogenèse concerne la croissance d'un organisme, d'un embryon à un individu adulte composé de dix mille milliards de cellules, dans le cas de l'être humain. Chaque cellule d'un être vivant contient un génome décrivant l'organisme entier, et servant à construire un corps, puis à le réparer en cas d'agression. Basé sur ce principe, le projet embryonique [142], développé au Laboratoire de Systèmes Logiques, a vu la naissance (si l'on puis dire) d'un nouveau concept de circuits électroniques réparables. Conçu pour implémenter des systèmes cellulaires sur la base de molécules électroniques, la mort de molécules et de cellules y est compensée par l'activation de parties de rechange du circuit.

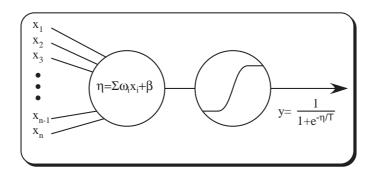

L'épigenèse, quant à elle, traite de l'apprentissage d'un individu, qui à partir de connaissances acquises, et en fonction de l'interaction qu'il entretient avec son environnement, développe un réseau de neurones impressionnant. Dans le cas de l'homme, il s'agit d'environ 10 milliards de neurones, chacun possédant jusqu'à 10'000 connexions. Il est bien clair que notre cerveau est une phénoménale machine à apprendre, et à mémoriser. Par simple observation, puis imitation, nous sommes capables d'acquérir de nouveaux savoirs. Là encore les ingénieurs se sont inspirés de ce concept en développant les réseaux de neurones artificiels, qui sont entre autre mis à contribution dans des applications de reconnaissance de formes ou de contrôle de robot.

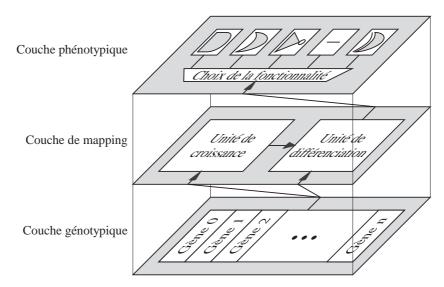

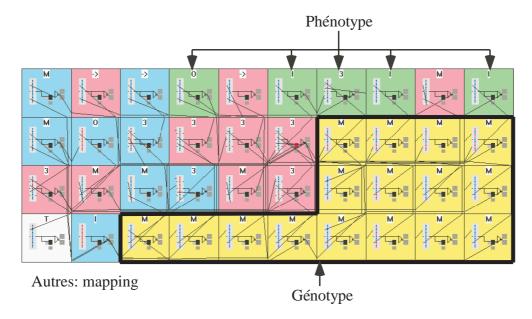

En comparaison des solutions logicielles, le matériel, de par son parallélisme intrinsèque, offre une accélération potentielle de tels systèmes, qui peuvent être gourmands en temps de calcul. Les circuits reconfigurables permettent d'embarquer des applications mettant en jeu ces différents axes du vivant, dans l'optique de disposer de plateformes matérielles bio-inspirées. Ils ne sont toutefois pas entièrement adaptés aux mécanismes tels que l'autoréparation et la plasticité. De là est né le projet européen dénommé "POEtic", dont le but était la réalisation d'un tissu électronique permettant l'implémentation efficace d'applications bio-inspirées incluant au moins un des trois axes présentés. Cette thèse s'est donc déroulée dans le cadre de ce projet de collaboration, où notre tâche principale fut de mener à bien la réalisation de la partie programmable du circuit POEtic, appelée sous-système organique. Nous tenons à citer ici les partenaires du projet, ainsi qu'une brève description de leurs tâches respectives :

- Le Laboratoire de Systèmes Logiques, où nous avons étudié divers systèmes ontogénétiques, et principalement défini le sous-système organique, qui se trouve être l'un des sujets principaux de la présente thèse.

- L'Université de Lausanne, où une équipe de neurobiologistes a défini un nouveau type de neurone à impulsion.

- Le Laboratoire de Systèmes Autonomes, de l'EPFL, où un système de codage morphogénétique, une alternative à la correspondance directe du génotype au phénotype, a été investigué. Une application robotique du réseau de neurones développé par l'Université de Lausanne utilisant le circuit POEtic y a également été réalisée.

- L'Université Polytechnique de Catalogne, où le microprocesseur ainsi que le layout électronique du circuit furent réalisés, sur la base des fichiers VHDL que nous leurs avons fournis concernant la partie reprogrammable. Ils réalisèrent également une implémentation matérielle du neurone défini par l'Université de Lausanne.

- L'Université de York, où un système immunotronique a été développé, de même qu'un mécanisme d'autoréparation cellulaire démontrant l'efficacité du circuit construit. Un outil d'édition schématique permettant de créer des designs pour POEtic y a également été réalisé.

- L'Université de Glasgow, sur l'axe mathématique, où le modèle de l'Université de Lausanne fut validé, grâce à une armada d'outils mathématiques.

Les circuits reconfigurables actuels, comme nous le verrons dans le chapitre 2, ne proposent pas de systèmes de routage dynamique permettant de connecter deux parties du circuit lors de l'exécution. En effet, leur structure est principalement composée d'éléments de base simples, reliés entre eux par un réseau d'interconnexions plus ou moins complexe. Ces connexions ne peuvent toutefois être programmées que par un contrôleur externe, lors de la configuration du circuit.

Les systèmes bio-inspirés, tels que les réseaux de neurones artificiels à topologie variable, peuvent nécessiter la création ou la destruction de connexions en cours de fonctionnement. De même, des systèmes montrant des propriétés de développement et d'autoréparation pourraient être réalisés, utilisant la propriété de création de connexions. Des cellules de rechange pourraient alors être dynamiquement reliées au système préexistant, en remplaçant des cellules dont le bon fonctionnement n'est plus assuré.

Les nanotechnologies, quant à elles, n'en sont qu'à leurs débuts, mais promettent de révolutionner la manière de concevoir des systèmes informatiques. Nous aurons, dans un futur proche, des circuits moléculaires contenant un nombre plus que conséquent d'éléments qu'il faudra pouvoir programmer. Dès lors, les mécanismes développementaux pourront prendre toute leur importance, afin de créer des systèmes capables de s'auto-organiser, et de s'auto-réparer<sup>1</sup>. La capacité de créer des chemins de données dynamiquement sera nécessaire, afin de disposer d'un maximum de flexibilité et de possibilités d'autoréparation.

Le manque de routage dynamique dans les circuits reconfigurables actuels et la nécessité d'en disposer dans les futurs nano-circuits nous amènent à explorer de nouvelles voies pour la réalisation de tels circuits. Il existe des algorithmes pour la découverte du chemin le plus court entre deux ou plusieurs points, la plupart étant séquentiels. Quelques solutions parallèles ont été proposées, mais aucune n'a encore été intégrée à un circuit reconfigurable. Cette thèse se propose donc d'explorer divers algorithmes pouvant être implémentés de façon parallèle, et d'en analyser les différentes caractéristiques.

Enfin, outre le routage dynamique, les systèmes bio-inspirés multicellulaires ont besoin, lors de phases de développement ou d'autoréparation, de pouvoir modifier le comportement des cellules qui le composent. Pour ce faire, le tissu électronique doit pouvoir s'auto-configurer, ce qui est une caractéristique inexistante dans les circuits reconfigurables commerciaux. Le sous-système organique de POEtic possède donc cette capacité, qui, couplée au routage dynamique, offre une plasticité matérielle aux applications qui y seront implémentées.

#### 1.3 Contributions

Partant du constat que la possibilité de router dynamiquement des signaux dans les circuits reconfigurables actuels n'existe pas, la présente thèse apporte les contributions suivantes :

- Les systèmes de routage dynamique existants ont été étudiés et commentés.

- Un algorithme de routage matériel distribué a été proposé et implémenté, dans lequel aucun contrôle centralisé n'est nécessaire. Il est basé sur une implémentation parallèle de l'algorithme de Lee [137].

- Un second algorithme a été implémenté, réalisant la même fonction que l'algorithme de Mikami-Tabuchi [156], qui effectue une recherche par lignes.

- Une amélioration des deux précédents algorithmes a été réalisée, de manière à réduire non pas la longueur des chemins créés, mais plutôt les problèmes de congestion.

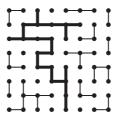

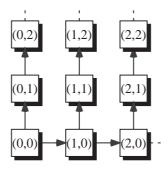

- Ces algorithmes, après avoir été implémentés pour un voisinage de 4, le furent pour les trois autres voisinages <sup>2</sup> réguliers à deux dimensions, à savoir 3, 6 et 8.

- Un dernier algorithme, n'exploitant que des liaisons locales afin d'améliorer la scalabilité du système, a également été réalisé.

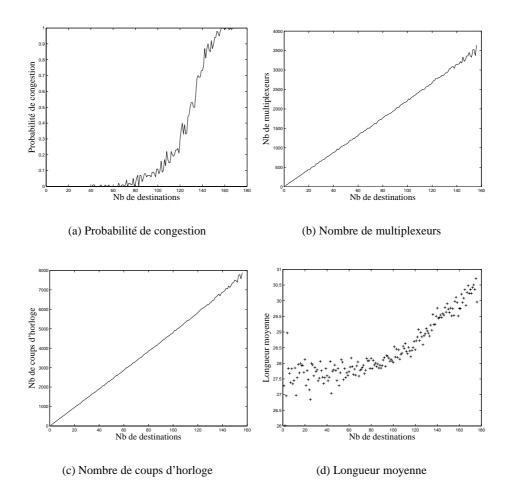

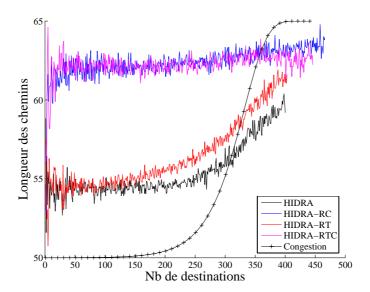

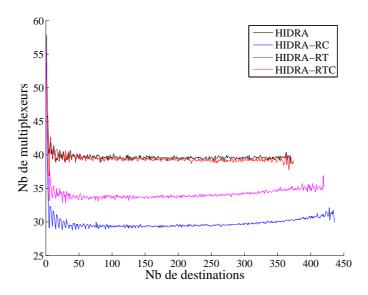

- Une comparaison des différents algorithmes sur le plan du temps d'exécution, de la congestion, du nombre de transistors nécessaires et de la longueur des chemins a été effectuée, de manière à pouvoir proposer la meilleure alternative en fonction de différentes contraintes.

<sup>&</sup>lt;sup>1</sup>Les systèmes moléculaires seront très probablement plus sujets aux fautes que les implémentations

<sup>&</sup>lt;sup>2</sup>Le voisinage désigne le nombre de voisines à laquelle une unité est reliée.

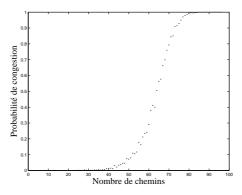

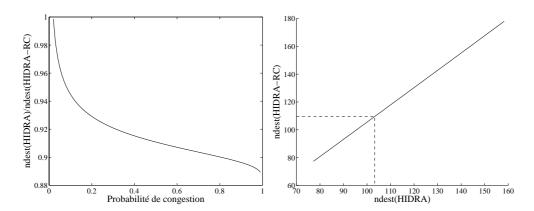

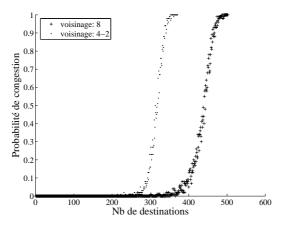

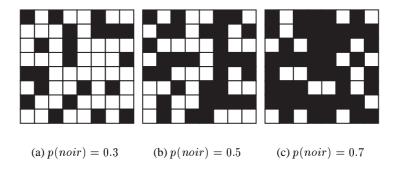

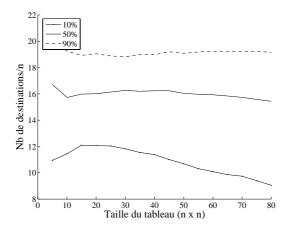

- Concernant la congestion, nous avons proposé un estimateur capable de l'approximer, de façon à pouvoir prédire les risques de congestion en fonction de plusieurs paramètres.

- De même, une comparaison des différents voisinages a été faite, afin de pouvoir choisir, en fonction notamment de la connectique et de l'espace disponible, la meilleure alternative.

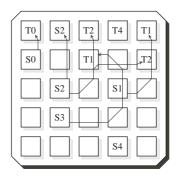

- Basée sur un des algorithmes proposés, la partie reconfigurable d'un nouveau circuit, qui fut physiquement réalisé, a été conçue. Elle offre, outre les fonctionnalités standard des circuits reconfigurables FPGAs, des possibilités de routage dynamique et d'auto-configuration partielle. Ce système reconfigurable possède de nombreuses caractéristiques qui en font une plateforme idéale pour y implémenter des applications bio-inspirées multicellulaires.

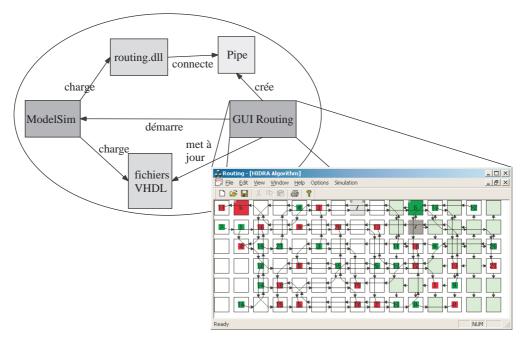

- Un logiciel permettant à un utilisateur de réaliser un design pour notre circuit a été réalisé. Il permet de configurer les éléments de base de la partie reconfigurable, de les connecter entre eux grâce à une interface graphique, et de visualiser les résultats d'une simulation du design.

- La manière de tirer avantage des capacités spécifiques du circuits a été démontrée, en proposant une solution pour l'implémentation de registres à décalage et de compteurs générateurs d'impulsions.

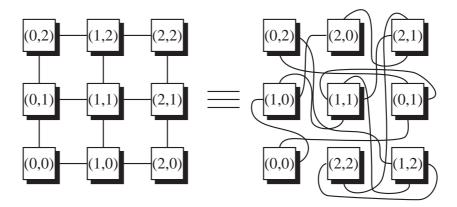

- Un mécanisme de développement basé sur un identifiant cellulaire a été proposé, puis implémenté sur ce nouveau circuit.

- Une démonstration a été faite sur la manière d'utiliser ce circuit pour réaliser une application de matériel évolutif au niveau des portes logiques, ainsi que dans le cadre d'évolution non-contrainte.

#### 1.4 Contenu de la thèse

Cette thèse est principalement divisée en 6 parties, outre cette introduction et la conclusion. Nous y présentons les systèmes bio-inspirés, puis les FPGAs et leurs limitations pour de tels systèmes. Le routage est ensuite introduit, avant d'entrer plus en détail dans les algorithmes développés dans le cadre de cette thèse. Finalement, un nouveau circuit reconfigurable, appelé POEtic, utilisant un de nos algorithmes de routage dynamique, est présenté, de même que différentes applications en démontrant l'utilité. La description succincte des chapitres est donnée ici :

- Le chapitre 2 présente les circuits reconfigurables (FPGAs, pour Field Programmable Gate Array) et leur évolution depuis les premiers circuits ne proposant que quelques portes logiques, jusqu'aux plus puissants FPGAs actuels qui exhibent des systèmes d'interconnexion des plus complexes. Leur limitation en terme de routage dynamique sera exposée, justifiant une partie de la présente thèse.

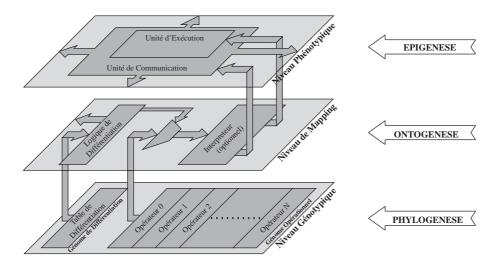

- Le chapitre 3 présente ce que sont les systèmes bio-inspirés, insistant sur les trois axes de la bio-inspiration, à savoir la phylogenèse, l'ontogenèse, et l'épigenèse. Il se termine par la présentation du projet POEtic, qui a pour but le développement d'un nouveau type de FPGA, un tissu POEtique, visant à faciliter l'implémentation d'applications bio-inspirées mettant en jeu des combinaisons des trois axes de la vie susmentionnés.

- Le chapitre 4 enchaîne tout naturellement sur le routage, en présentant les travaux déjà effectués sur des problèmes tels que la recherche du plus court chemin

- entre deux points. Nous y introduisons les premières solutions logicielles, puis les systèmes matériels qui ont déjà été développés.

- En se basant sur les systèmes de routage présentés, le chapitre 5 introduit nos solutions. Les différentes architectures développées sont détaillées, et des tests de vitesse, de taille et de congestion sont effectués pour chaque algorithme, ainsi que pour les différents voisinages.

- Le chapitre 6 présente en détail l'architecture du circuit réalisé. Un accent particulier est mis sur la partie reconfigurable du circuit, qui fut développée dans le cadre de cette thèse. De plus, nous explicitons la manière dont certaines de ses caractéristiques peuvent efficacement implémenter certains composants de base tels que des registres à décalage ou des compteurs générateurs d'impulsions.

- Ayant défini le circuit, nous nous penchons, dans le chapitre 7, sur son efficacité quant à l'implémentation de mécanismes phylogénétiques, ontogénétiques, et épigénétiques. Ce chapitre démontre notamment l'utilité du routage dynamique et de la reconfiguration partielle.

- Finalement, la conclusion résume nos travaux, explicite les limitations du routage distribué et du circuit POEtic, et propose des extensions aux systèmes développés, qui pourraient être utiles à une potentielle deuxième version du circuit.

# De la configuration des circuits électroniques

Seul l'éphémère dure. Eugène IONESCO

ES CIRCUITS électroniques envahissent le quotidien de manière impressionnante. Ils sont présents dans les machines à laver, les montres, les voitures, et évidemment dans les ordinateurs. Qui aurait pensé, le 23 décembre 1947, date de la création du premier transistor par William Shockley, Walter Braittain et John Bardeen, physiciens des laboratoires Bell, qu'en 55 ans l'électronique allait révolutionner le style de vie de l'humanité?

En 1952, G. W. A. Dummer, un Anglais expert en radar, publia un article proposant d'utiliser un bloc de matériel solide pour connecter des composants électroniques, sans fils de connexions. Le concept de circuit intégré était né, et six ans plus tard, en 1958, Jack Kilby, travaillant pour Texas Instruments, en réalisa le premier spécimen, sous la forme d'un oscillateur à décalage de phase contenant cinq éléments sur une seule pièce de semi-conducteur. Depuis lors, la complexité des circuits intégrés n'a cessé de croître, pour arriver à des systèmes jusqu'à 1.7 milliard de transistors pour le dernier processeur d'Intel.

La fabrication d'un circuit intégré spécifique à une application (ASIC) est une tâche ardue et coûteuse en temps et en argent. En effet, la réalisation d'un prototype nécessite la création d'un ou plusieurs masques<sup>1</sup>, qui sont très coûteux s'il ne sont destinés qu'à une petite quantité. De plus, une simple erreur dans le design du système implique la création d'un ou plusieurs nouveaux masques. Et finalement, l'investissement en temps de développement est important, et n'est pas forcément tolérable si un produit doit très rapidement être mis sur le marché.

Parallèlement à l'avancée des ASICs, divers circuits programmables ont fait leur apparition, afin de réduire le temps et le coût de développement des circuits électroniques, tout en restant relativement compétitifs sur le plan de la rapidité d'exécution.

<sup>&</sup>lt;sup>1</sup>Un masque sert à apposer des couches de métal sur le silicium, dans l'optique de relier entre eux les divers éléments tels que les transistors (ce type de technique est également exploitée pour le dopage du silicium).

La question est alors de pouvoir concevoir des systèmes contenant des circuits intégrés de la manière la moins coûteuse en terme de temps et d'argent. En fonction de différents paramètres tels que la complexité du système, le nombre de pièces à fabriquer ou le temps imparti, un type d'implémentation est choisi parmi la gamme des possibilités.

Concernant les systèmes bio-inspirés, qui seront introduits dans le chapitre suivant, un nombre non négligeable d'applications ont mis en jeu des circuits programmables : à titre d'exemples, le large parallélisme des réseaux de neurones s'applique parfaitement à une implémentation matérielle [56], et certains chercheurs travaillent à un nouveau type de systèmes informatiques tolérants aux pannes [142] dont les prototypes nécessitent la possibilité de se reprogrammer.

Dans ce chapitre, nous allons évoquer les différents types de circuits intégrés non-programmables, programmables et reprogrammables, allant de la simple mémoire programmable au circuit FPGA (Field Programmable Gate Array) [33] de plus de 10 millions de portes logiques reprogrammables, en passant par les circuits logiques programmables simples et les circuits spécifiques à une application. Nous allons tout d'abord présenter brièvement les processeurs puis les différents types de circuits ASICs. Ensuite nous présenterons les technologies de programmation matérielle existantes et l'évolution des circuits programmables PLD (Programmable Logic Device), en suivant un ordre chronologique, jusqu'à arriver aux FPGAs, qui feront l'objet d'une attention toute particulière. L'optique de cette thèse étant de proposer une nouvelle FPGA possédant des possibilités de routage et d'auto-configuration non présentes dans les circuits commerciaux, la description de tous les circuits se fera en mettant un accent particulier sur leurs possibilités et limitations en terme de routage.

#### 2.1 Processeur

Un processeur [185] est un circuit intégré permettant d'implémenter n'importe quelle fonction en exécutant de manière séquentielle un code compilé. Le grand avantage du processeur est sa généricité, puisque n'importe quel programme peut y être exécuté. De plus, il est très facile de le programmer, c'est-à-dire de transcrire dans le langage du processeur un problème particulier.

Malheureusement, cette généricité s'accompagne d'un coût, à savoir le temps d'exécution d'une tâche. En effet, les instructions sont exécutées une à une (bien que certains processeurs présentent un certain parallélisme), l'opération a+2+b+d nécessitant au minimum trois pas de temps. Un système matériel peut, lui, effectuer cette opération en un seul pas. De plus, le processeur étant une unité chargée d'un calcul, une seule erreur compromet l'ensemble de son exécution. Les systèmes parallèles laissent quant à eux la porte ouverte à l'autoréparation, une unité pouvant potentiellement prendre la place d'une autre se trouvant dans un état défectueux.

Les applications intrinsèquement parallèles tels que les réseaux de neurones ou les automates cellulaires sont donc exécutées de manière séquentielle par un processeur, alors qu'un système matériel a la possibilité d'exploiter tout le parallélisme possible. Les systèmes cellulaires composés de plusieurs cellules effectuant des tâches en parallèle sont donc bien plus efficacement réalisés en matériel qu'en logiciel. C'est pourquoi le reste de cette thèse traite de matériel, en enchaînant directement sur les ASICs, une des solutions d'implémentation de tels systèmes.

2.2. ASIC 9

#### **2.2 ASIC**

Le Circuit Intégré Spécifique à une Application (ASIC) [219] est une des manières de réaliser un système de calcul matériel. Pour chaque application, un circuit différent est créé, soit en le construisant entièrement, soit en configurant une grille d'éléments préconstruits. L'avantage des ASICs sur les circuits reconfigurables, pour une même technologie, est évidemment leur rapidité, puisque les connexions sont créées physiquement plutôt que programmées. Toutefois, leur force est également leur faiblesse, puisque leur conception nécessite plus de temps, étant donné qu'en tout cas une couche de métal doit être apposée. De plus, ils ne sont en aucun cas programmables, et une erreur dans le design implique un changement complet du circuit.

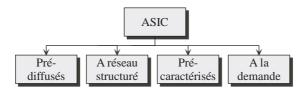

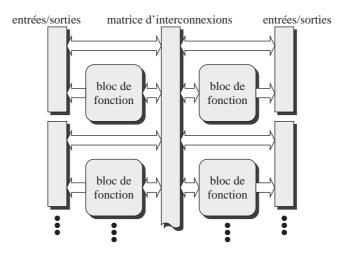

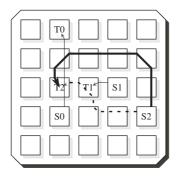

Quatre grandes classes d'ASICs sont présentées ici, le graphique 2.1 les exposant avec un niveau de complexité croissant de gauche à droite. Nous allons les détailler dans l'ordre chronologique de leur apparition.

Figure 2.1 : Les différents types de circuits ASIC.

#### 2.2.1 A la demande

Pour la création d'un ASIC à la demande, communément appelé Full-Custom [48], les ingénieurs contrôlent chaque élément du circuit fabriqué. Ils dessinent les transistors, les placent et les connectent, sans qu'aucune contrainte prédéfinie n'existe concernant le placement des éléments. La taille de chaque transistor peut être changée afin d'optimiser le fonctionnement du système. L'avantage de cette approche est l'efficacité du circuit final en terme de quantité de silicium et de vitesse. En effet, il est possible de placer les éléments de manière optimale, sans aucune perte de place, et de le faire en tenant compte des contraintes de temps d'exécution. Par contre, si une erreur s'est subrepticement glissée dans la conception, le dessin du circuit entier doit être revu, dans un long et coûteux processus de correction. Ce type d'ASIC n'est donc pas du tout adapté au prototypage, étant donné le temps et l'investissement nécessaire à chaque prototype.

Les possibilités de routage dans un tel circuit sont quasiment infinies, étant donné que le développeur a total contrôle sur toute la conception du circuit. La seule limitation intervient par le nombre de couches de métal apposées sur le silicium. Toutefois, ce routage est fixé une fois pour toutes, ne laissant aucune possibilité de modification ultérieure.

#### 2.2.2 Prédiffusés

Dans le milieu des années 60, Fairchild Semiconductor créa le précurseur des tableaux de portes, sous la forme d'un circuit appelé Micromatrix, composé d'une centaine de transistors. Les ingénieurs devaient dessiner à la main les interconnexions sur des feuilles de plastique, pour réaliser un circuit spécifique. Ensuite, en 1967, un nouveau circuit, appelé Micromosaic, et contenant quelques centaines de transistors, fut proposé par la même société, avec cette fois-ci un programme capable de générer automatiquement les interconnexions en fonction des spécifications des ingénieurs. Ce sont toutefois les compagnies telles qu'IBM et Fujitsu qui développèrent le concept d'ASIC prédiffusé (ou à tableau de portes)<sup>2</sup>.

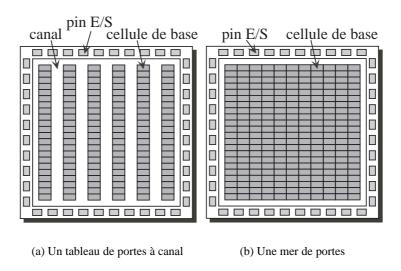

Dans le cas des mers de portes [99], les vendeurs fabriquent un circuit composé d'un tableau de cellules de base tels que des transistors. Une deuxième variante, le tableau de portes avec canaux de routage, propose plusieurs rangées de ces cellules séparées par des canaux de routage pouvant être connectés à ces éléments (Figure 2.2). La connectique interne à une rangée permet de créer des modules simples du type multiplexeurs ou bascules, et les canaux de routage offrent la possibilité de connecter ces modules entre eux. Le fabricant fournit généralement une librairie de modules, que le développeur peut utiliser, et qui sont ensuite placés sur le tableau en connectant les éléments de base grâce a des couches de métal supplémentaires.

Figure 2.2 : Deux types de circuits prédiffusés.

L'un des avantages des circuits prédiffusés est que le vendeur peut fabriquer une grande quantité de pré-circuits identiques, et qu'il n'est nécessaire, pour réaliser un circuit final, que d'ajouter des couches de métal, sans se soucier de la préparation du silicium. En contrepartie, il y a souvent un nombre non négligeable d'éléments de base inutilisés, le placement des transistors étant contraint dans le sens où ils sont déjà incrustés dans le silicium, et le routage n'est donc pas optimal. Ces différents facteurs font que le tableau de portes est nettement moins efficace qu'une implémentation full-custom en terme de consommation et performance. Il offre cependant un temps de réalisation nettement plus faible, et également un moindre coût.

<sup>&</sup>lt;sup>2</sup>En anglais *gate array*, et *sea of gates* pour mer de portes. Connu également sous l'appelation MPGA pour Metal Programmable Gate Array ou Mask Programmable Gate Array.

#### 2.2.3 Pré-caractérisés

Les ASIC pré-caractérisés (en anglais Standard Cell)[220] ont vu le jour au début des années 80, dans le but de combler les lacunes des circuits prédiffusés. Contrairement à ces derniers, le silicium n'est pas prédiffusé avec des éléments de base. Le vendeur propose ici une librairie de cellules de base, ainsi que des modules plus complexes tels que des RAMs, des microprocesseurs, et bien d'autres. Le développeur utilise alors ces divers éléments pour créer une liste de modules et de leurs interconnexions décrivant son système, et le vendeur se charge ensuite de créer le circuit intégré.

L'avantage de cette approche réside dans l'optimisation des modules fournis par le fabriquant. Le placement de ces modules est réalisé de manière à également optimiser les performances, tout en minimisant la place nécessaire sur le silicium. Dès lors, la solution pré-caractérisée est très proche de l'optimal obtenu grâce à l'approche full-custom, et nécessite un temps de développement nettement moindre.

#### 2.2.4 A réseau structuré

Comme nous le verrons à la section suivante, les circuits reconfigurables ont l'avantage d'être d'excellents candidats pour les applications industrielles de petit volume ainsi que pour le prototypage, un design pouvant être immédiatement testé. Toutefois, ils ne peuvent, en terme de vitesse, rivaliser avec un circuit ASIC spécialement conçu pour une application. C'est pourquoi en 2003 le dernier-né des circuits programmable a fait son apparition<sup>3</sup>: l'ASIC à réseau structuré [257].

Un ASIC à réseau structuré consiste en un circuit composé de différents éléments semblables à ceux que l'on peut trouver dans un FPGA standard, tels que look-up tables <sup>4</sup>, inverseurs, flip-flops, et bien d'autres. Toutefois, à l'inverse du FPGA, ces différents blocs ne sont pas connectés entre eux. Par analogie avec les mers de portes, on pourrait les appeler mers de macros, des modules de complexité supérieure étant prédiffusés. Le circuit de base créé, il reste donc des couches de métal disponibles qui permettent de réaliser la connectique nécessaire à la réalisation d'un design particulier.

Certains fabricants proposent des solutions mettant en jeu des look-up tables et différentes portes logiques, ainsi que des blocs de mémoire, des DLLs (Delay-Locked Loops) et des PLLs (Phase-Locked Loops). Les outils de conception, responsables de la synthèse et du placement-routage, sont petit à petit adaptés à cette nouvelle technologie. Altera, un des leaders du marché du FPGA, offre quant à lui le concept de HardCopy, un circuit contenant exactement les mêmes éléments de base que les FP-GAs qu'il propose sans toutefois qu'ils soient interconnectés. A l'heure actuelle, les circuits Stratix, APEX 20Ke et APEX 20KC supportent cette solution. Un utilisateur ayant réalisé et testé un système sur un de ces FPGAs peut alors le transférer sur un ASIC structuré correspondant, en étant sûr de garder la même fonctionnalité tout en augmentant potentiellement la fréquence de fonctionnement.

A ce jour peu de tests ont été effectués dans le but de comparer cette méthodologie avec d'autres, mais les résultats préliminaires tendent à prouver que les ASICs à réseau structuré occupent trois fois plus de place que les ASICs pré-caractérisés, et consomment deux à trois fois plus [146].

<sup>&</sup>lt;sup>3</sup>Notons toutefois que le concept est apparu au début des années 90, sans connaître grand succès.

$<sup>^4</sup>$ Une look-up table, ou table de correspondance en français, fait correspondre une sortie à chaque combinaison d'entrées. Dans nos systèmes digitaux, nous parlerons de k-LUT pour une look-up table à k entrées. Dans ce cas,  $2^k$  bits définissent la sortie pour chacune des combinaisons possibles des entrées.

#### 2.2.5 Limitations

Les quatre types d'ASIC présentés sont tous des circuits fixes, qui une fois réalisés n'offrent aucune souplesse, leur fonctionnalité étant définitivement figée. L'avantage de cette approche est la rapidité du circuit final, ainsi que la place nécessaire à l'implémentation d'un design particulier. Toutefois, la non-reprogrammabilité de tels circuits est un important obstacle au prototypage, une réalisation physique pouvant demander jusqu'à 4 mois. De plus, la fixité de tels circuits ne permet pas la conception de systèmes adaptables, capables d'évoluer en fonction d'une tâche à résoudre dans un environnement qui peut être changeant. C'est pourquoi nous allons maintenant présenter les circuits programmables, qui se proposent de pallier au manque de flexibilité des ASICs. Nous allons tout d'abord présenter les différentes technologies de programmation avant d'aborder les circuits programmables dans l'ordre chronologique de leur apparition sur le marché, correspondant également à l'ordre de complexité.

#### 2.3 Technologies de programmation

N'ayant pas peur des truismes, commençons par constater qu'un circuit programmable doit pouvoir être programmé, de même qu'un circuit reprogrammable doit pouvoir être reprogrammé. Nous allons donc présenter ici différentes technologies servant à la réalisation de circuits programmables ou reprogrammables. Nous commencerons par les masques, les fusibles et les antifusibles, non reprogrammables, puis nous enchaînerons sur les technologies reprogrammables, à savoir l'EPROM, l'EEPROM, la FLASH et la SRAM.

#### **2.3.1** Masque

Comme nous l'avons vu précédemment, certains circuits ASIC (prédiffusés et à réseau structuré) peuvent être programmés grâce à un masque. Ce procédé, qui est également utilisé pour la création de mémoires à lecture seule (ROM), consiste à fabriquer un circuit intégré en y plaçant les composants et quelques ou aucune couche de métal. Ensuite, l'ajout d'une ou plusieurs couches de métal supplémentaires suffit à définir exactement la fonctionnalité du circuit. Un ou des masques sont donc générés pour chaque circuit différent, et servent à imposer les dernières couches de métal.

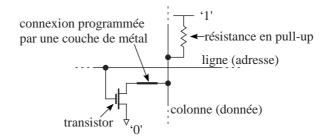

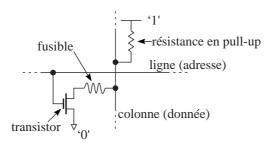

Dans le cas d'une mémoire ROM, qui n'est accessible qu'en lecture, après sa réalisation, toutes ses connexions sont figées. Il est possible de créer une ROM spécifique à partir de rien, ou de la préconstruire et d'utiliser la technique de masquage. Dans ce deuxième cas, une cellule mémoire est semblable à celle de la figure 2.3, où l'ensemble de la mémoire est répartie en ligne/colonne, la ligne servant d'adresse, et la colonne de donnée, une seule ligne pouvant être active à un instant donné. La programmation se fait par l'ajout d'une couche de métal, connectant certains transistors à leur colonne, une résistance en pull-up forçant la valeur à '1' si la connexion n'est pas établie, ou si le transistor est ouvert. Dans le cas de l'activation d'une ligne, chaque cellule de la ligne active fournit à sa colonne la valeur mémorisée, qui dans notre exemple, est un '1' si la connexion n'est pas programmée, et '0' sinon.

Notons que la réalisation d'un circuit par masquage offre un avantage en terme de délais, ces circuits étant les plus rapides des circuits programmables. Cependant

Figure 2.3 : Une cellule de mémoire ROM programmée par masque, basée sur un transistor.

le fait de devoir appliquer des couches de métal est un processus long et coûteux en comparaison des autres techniques.

#### 2.3.2 Fusible

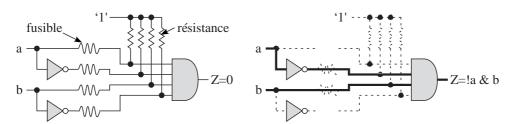

Basé sur le même principe que les fusibles domestiques, qui, pour éviter la destruction de nos appareils électroménagers, sont détruits par un trop fort courant, la technologie basée sur des fusibles fut une des premières à être utilisée. Le principe est simplement d'avoir des fusibles sur certains fils, et d'en faire brûler certains en leur appliquant un courant trop important. Sur chacun de ces fils, une résistance en pull-up ou pull-down force la valeur à 1 ou à 0 si le fusible a été détruit, comme illustré à la figure 2.4.

Figure 2.4 : Un circuit contenant 4 fusibles non programmés, puis le circuit résultant après avoir brûlé le premier et le quatrième fusible.

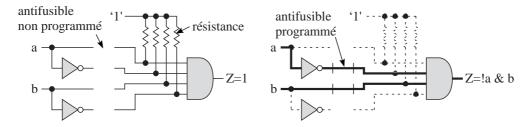

#### 2.3.3 Antifusible

A ce que l'on peut considérer comme l'opposé des fusibles, se trouvent les antifusibles. De la même manière, sur certains fils du circuit se trouvent des antifusibles, mais contrairement aux fusibles, lorsqu'ils ne sont pas programmés, ils agissent comme une résistance infinie, comme si le fil était coupé. En appliquant un fort courant de grand voltage, l'antifusible est programmé, et laisse dès lors passer le courant. Une résistance est également placée après chaque antifusible, de manière à forcer la ligne à 1 ou 0 dans le cas où il n'est pas programmé (Figure 2.5).

Notons que les circuits à base de fusibles et d'antifusibles ne peuvent être programmées qu'une seule fois. Chaque nouvelle implémentation, en cas d'erreur de design par exemple, implique dès lors la programmation d'un nouveau composant et l'élimination de l'ancien. Cependant, cette programmation étant électrique, un simple appareil

Figure 2.5 : *Un circuit contenant 4 antifusibles non programmés, puis le circuit résultant d'une programmation.*

est nécessaire, rendant le processus nettement plus simple et rapide que le masquage.

#### **2.3.4 EPROM**

Avant de décrire la technologie EPROM, passons quelques instants sur le concept de mémoire PROM. Le fonctionnement d'une mémoire PROM est identique que celui d'une ROM, si ce n'est le mode programmation. Au lieu de devoir physiquement créer des connexions grâce à une couche de métal, un fusible peut être brûlé ou non, ce qui est nettement plus rapide et moins coûteux (Figure 2.6). En effet, lors de la réalisation d'un système informatique, il n'est pas rare que des erreurs se glissent dans un design, et la destruction d'une PROM à chaque erreur n'est pas la panacée.

Figure 2.6 : Une cellule de mémoire PROM, basée sur un transistor et un fusible.

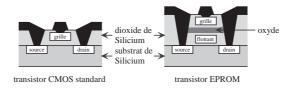

La technologie de type Erasable Programmable Read-Only Memory (EPROM), introduite en 1971 par Intel est dès lors une nette amélioration de la PROM sur le plan de la flexibilité, puisqu'elle permet une reprogrammation du circuit. Il s'agit d'un nouveau type de transistor, basé sur un transistor MOS, auquel une couche de silicium polycristallin, appelé porte flottante, a été ajoutée, isolée par des couches d'oxyde (Figure 2.7). Dans son état initial, le transistor agit normalement, tel un MOS standard. En appliquant un courant de haut voltage (typiquement 12V) entre la grille et le drain, un effet tunnel charge la porte flottante en électrons, ce qui a pour effet de bloquer le transistor en état ouvert. A la suite de la programmation, quelle que soit la tension appliquée au contrôle, aucun courant ne peut passer entre la source et le drain. La charge créée par la programmation perdure, même lorsque le circuit est hors tension, et ce n'est qu'avec une exposition du circuit à des rayons UV que la programmation est effacée. Lié à l'effacement, un des désavantages de l'EPROM est qu'une fenêtre en quartz doit être apposée sur le circuit, afin de pouvoir laisser passer les rayons UV, ce qui augmente grandement le prix du boîtier.

Figure 2.7: Un transistor CMOS standard et un transistor EPROM.

#### 2.3.5 EEPROM/Flash

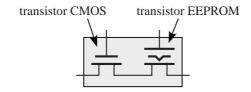

Le principal inconvénient des EPROMs, la déprogrammation par rayons UV, est oublié dans les EEPROMs, qui sont effaçables électriquement. Il n'est dès lors plus nécessaire d'intervenir physiquement avec de la lumière UV, un système électronique pouvant reprogrammer l'EEPROM de manière autonome. Sur le plan de l'espace pris sur le silicium, une cellule mémoire d'EEPROM occupe toutefois environ 2,5 fois plus de place qu'une cellule d'EPROM, car elle est composée de deux transistors, ainsi que de l'espace nécessaire entre eux deux (Figure 2.8).

Figure 2.8 : *Une cellule mémoire EEPROM*.

Les mémoires FLASH [24] sont basées sur le même principe d'effacement électronique et de non-volatilité. De nombreuses expériences et implémentations en ont fait des composants très largement utilisés à l'heure actuelle. Vues de l'extérieur, les FLASH sont quasiment identiques aux EEPROMs, si ce n'est que l'effacement se fait par secteur, et non octet par octet. Elles sont toutefois souvent préférées, de par leur vitesse et leur taille, qui peut être plus imposante que celle des EEPROMs.

#### 2.3.6 **SRAM**

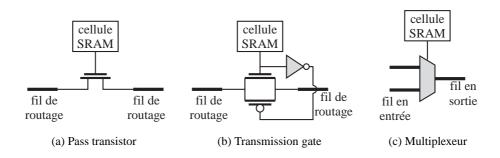

La technologie SRAM, pour Static Random Access Memory, est, contrairement à celles déjà présentées, volatile, et doit donc être reprogrammée à chaque remise en marche du système. Leur second désavantage réside dans la place nécessaire à une cellule, qui est composée de quatre à six transistors formant un latch (Figure 2.9).

Figure 2.9: Une cellule mémoire SRAM.

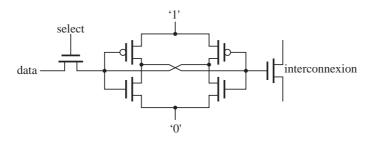

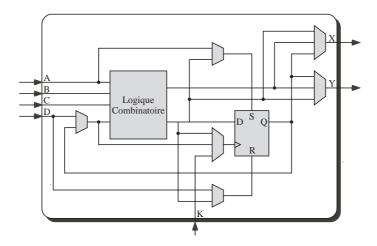

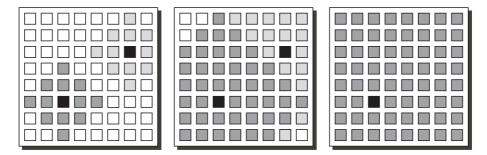

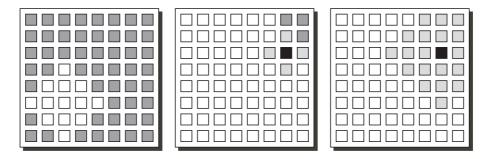

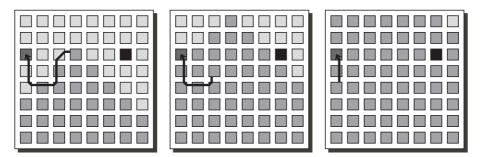

Toutefois, la grande facilité de programmation des circuits en technologie SRAM en a fait le choix privilégié des deux plus grands fabricants de FPGAs, à savoir Xilinx et Altera. La figure 2.10 illustre les différentes manières d'utiliser des cellules de mémoire SRAM pour la réalisation de circuits programmables. Les FPGAs commerciaux basés sur cette technologie sont le plus souvent implémentés avec des pass-transistors ou des portes de transmission. Seul le fameux XC6200, que nous décrivons à la page 23 est réalisé avec des multiplexeurs. Cette dernière technique offre l'avantage d'interdire tout court-circuit, contrairement aux deux autres. Toutefois, cet avantage se paie par une baisse de performances en terme de rapidité, un signal mettant plus de temps à passer un multiplexeur qu'un simple transistor.

Figure 2.10 : Trois technologies de programmation associées à la RAM statique.

#### **2.3.7 Résumé**

Nous avons présenté différentes technologies utilisées dans le cadre des circuits programmables. Le tableau 2.1 résume les caractéristiques des trois principales techniques utilisées dans les circuits programmables. Les antifusibles sont d'excellents candidats pour les systèmes nécessitant une très haute fréquence d'horloge, mais ont le très net problème de ne pouvoir être reprogrammés. Les fusibles ne sont plus utilisés, étant donné qu'ils sont couplés à une technologie bipolaire, qui n'est plus d'actualité. Les technologies EPROM et EEPROM permettent cette reprogrammation, mais au coût d'une intervention humaine et un temps d'effacement de une à quinze minutes pour les premières, et d'un temps d'effacement non négligeable pour les deuxièmes, ainsi que d'une forte tension, de l'ordre de 12V pour la reprogrammation. Les cellules SRAM, quant à elles, sont très rapidement reprogrammables, au coût d'une plus grande place occupée et de leur volatilité.

| Type              | <b>EPROM</b> | Antifusible | SRAM |

|-------------------|--------------|-------------|------|

| Rapidité          | _            | +           | _    |

| Densité           | _            | +           |      |

| Facilité          | +            | _           | +    |

| Reprogrammabilité | +            | _           | ++   |

Tableau 2.1 : Comparaison des caractéristiques des différentes technologies.

#### 2.4 Circuits logiques programmables

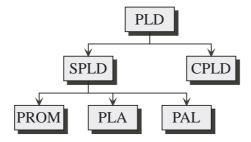

Les circuits programmables sont apparus en 1970, et depuis se sont complexifiés de manière spectaculaire. Il existe dans la littérature plusieurs manières de les classer, certains considérant que les CPLDs (Complex Programmable Logic Device) ne sont pas un sous-ensemble des PLDs (Programmable Logic Device). Nous choisirons toutefois l'approche illustrée à la figure 2.11 consistant à séparer les PLDs en deux sous-classes, à savoir les SPLDs (Simple Programmable Logic Device) et les CPLDs.

Figure 2.11: Une classification des circuits logiques programmables.

Nous allons décrire les différents types de circuits programmables, dans l'ordre chronologique de leur apparition, correspondant également à leur complexité, en commençant par les SPLD, les CPLDs, puis les FPGAs.

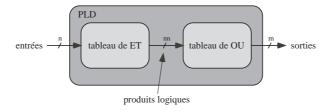

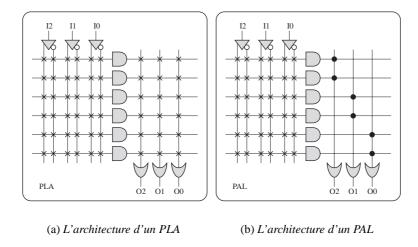

#### 2.4.1 SPLD

Les SPLDs (Simple Programmable Logic Device)[36], dans une description haut niveau, sont composés d'une grille de portes ET et d'une grille de portes OU, les deux étant reliées. Les entrées du système peuvent être connectées aux portes ET, et le résultat des portes OU correspond à la sortie du système (Figure 2.12). Dans ces circuits, les connexions sont préexistantes, les différentes lignes étant reliées par des fusibles, des transistors EPROM, ou des transistors EEPROM. En brûlant certains de ces fusibles, ou en programmant les transistors, il est alors possible de réaliser différentes fonctions logiques.

Figure 2.12: L'architecture d'un SPLD.

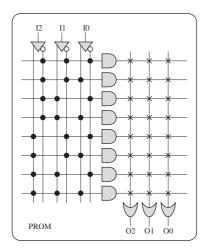

#### **PROM**

Les premiers circuits programmable à avoir vu le jour sont les PROMs (Programmable Read-Only Memory) (Figure 2.13), le terme PROM étant introduit en 1970. Ces circuits sont des mémoires accessibles en lecture, qui contrairement aux ROMs, sont programmables. En effet, une ROM est livrées déjà configurée, et ne peut être accédée

Figure 2.13: L'architecture fonctionnelle d'une PROM.

qu'en écriture, alors qu'une PROM est une mémoire vide, qui peut être écrite, une seule fois, par l'utilisateur. Après cette unique écriture, une PROM se comporte exactement comme une ROM. Ces circuits, qui ne sont pas reprogrammables, sont répartis en deux sous-classes, les Mask-Programmable Chips, programmés par le fabricant, et les Field-Programmable Chips, qui sont programmés par l'utilisateur.

Notons également qu'à l'origine les PROMs étaient vouées à faire office de mémoire d'instruction pour les ordinateurs. Leur emploi s'est toutefois généralisé puisqu'on les a utilisées pour l'implémentation de fonctions logiques simples tels que des look-up tables ou des machines d'état. Les PROMs se sont très vite imposées dans ce domaine, de par le fait qu'elles étaient plus petites, moins lourdes, moins chères, et moins sujettes aux erreurs que les systèmes composés de plusieurs circuits comportant des portes logiques. De plus, une erreur de design pouvait être rapidement modifiée en programmant une nouvelle PROM, ce qui était nettement plus rapide et simple que de modifier un circuit imprimé.

L'avantage des PROMs sur les autres PLDs est leur efficacité pour l'implémentation de fonctions logiques nécessitant un grand nombre de produits, mais elles ont le désavantage de n'accepter qu'un nombre limité d'entrées, étant donné que toutes les combinaisons possibles des entrées sont décodées (la figure 2.13 illustre ce décodage par la partie ET et la programmation de la partie OU).

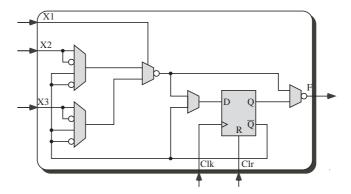

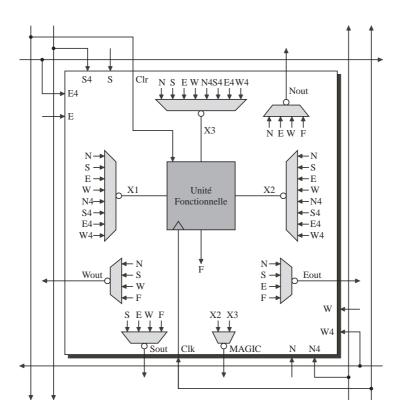

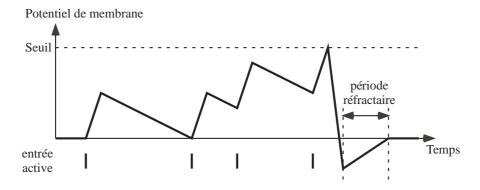

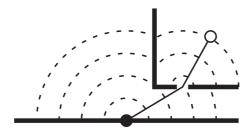

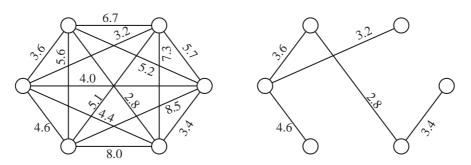

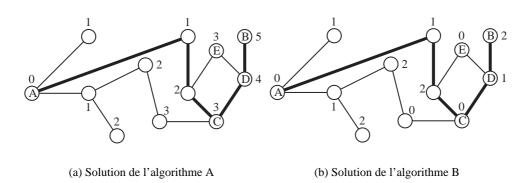

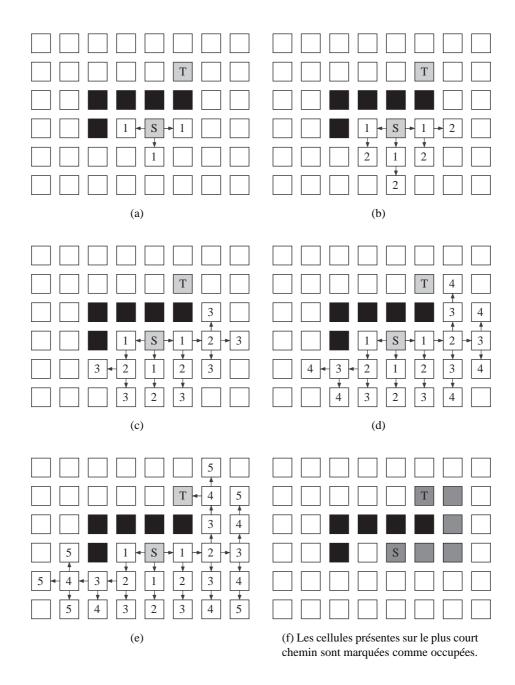

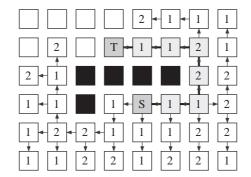

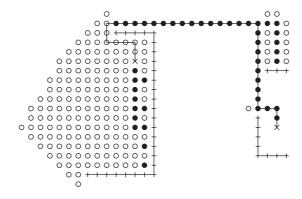

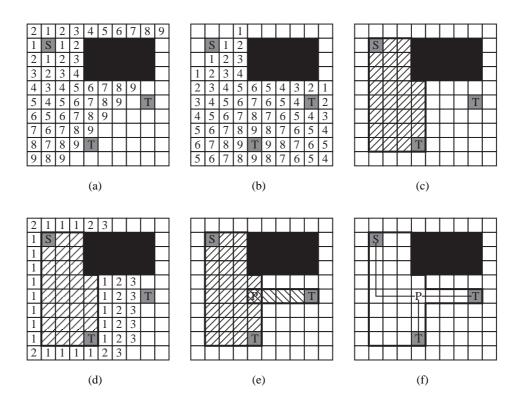

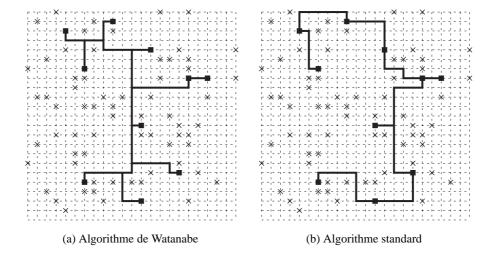

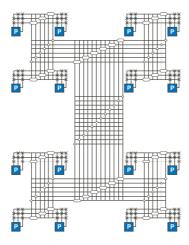

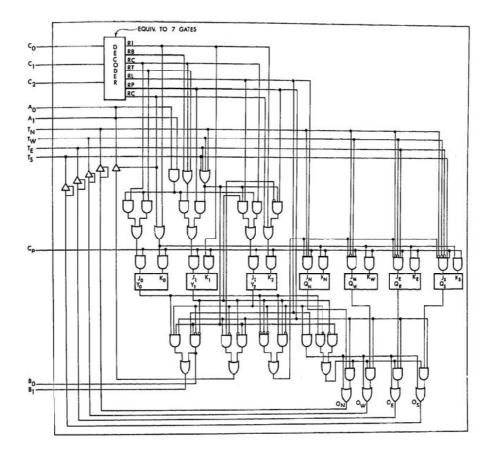

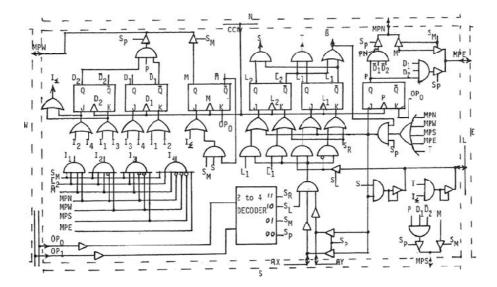

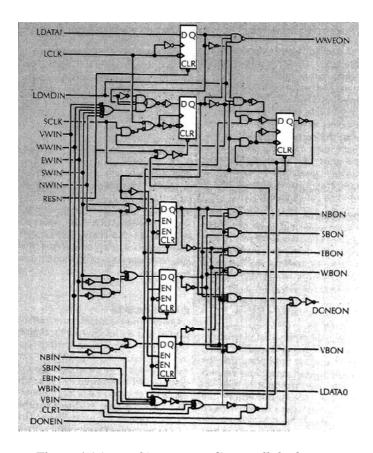

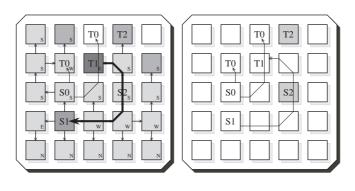

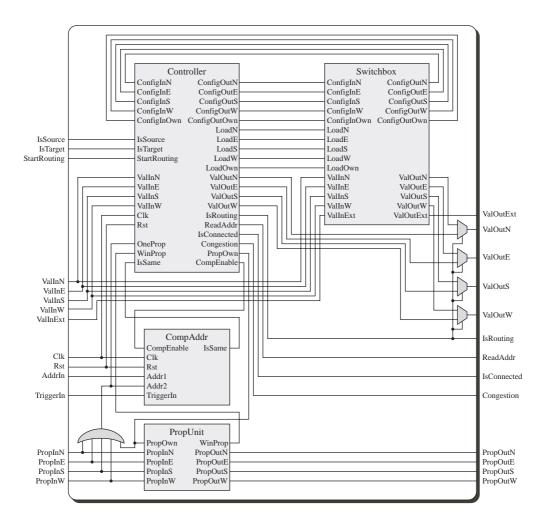

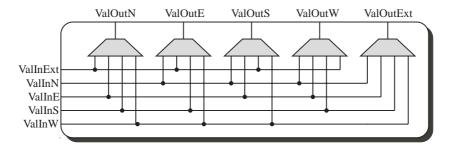

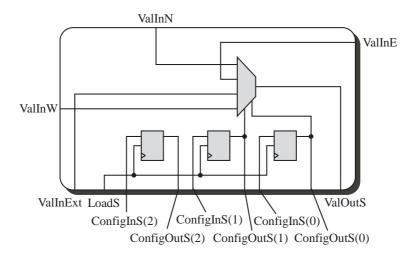

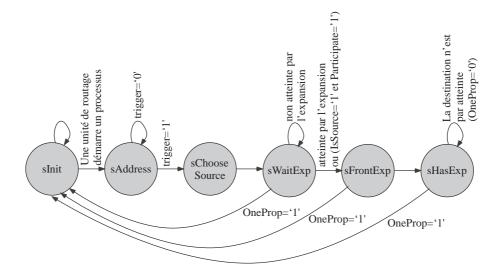

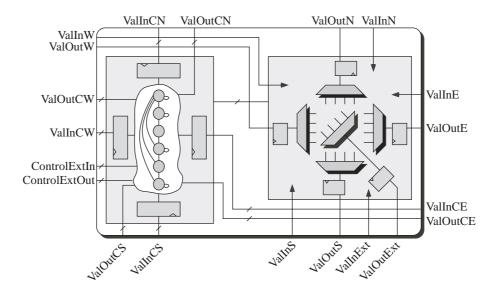

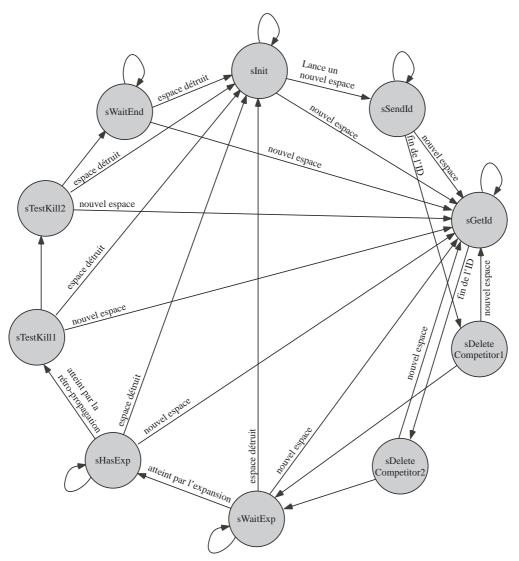

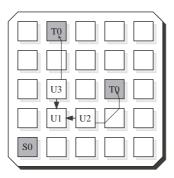

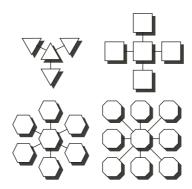

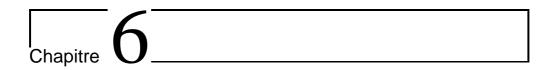

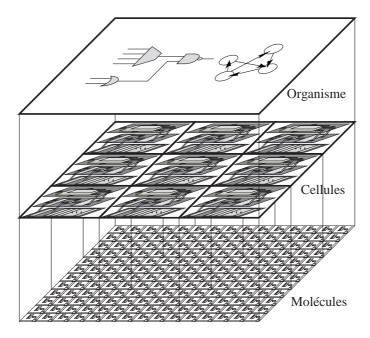

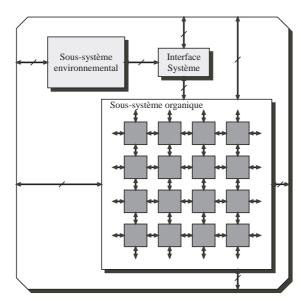

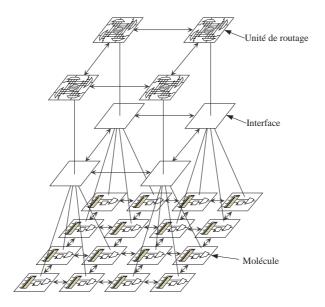

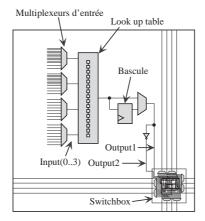

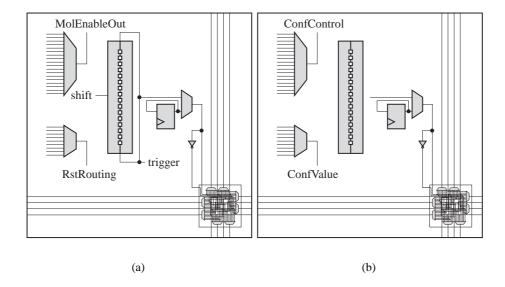

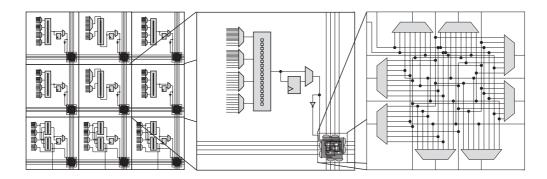

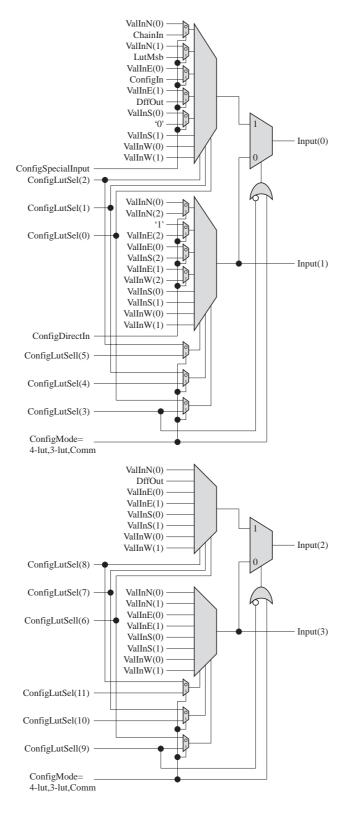

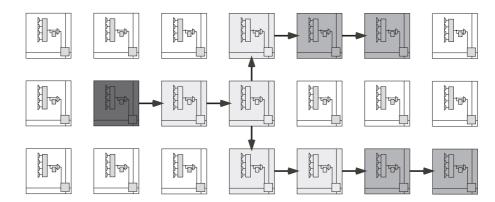

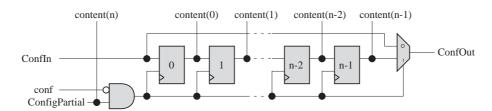

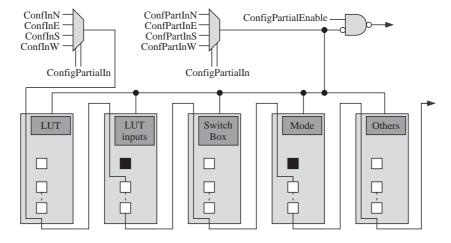

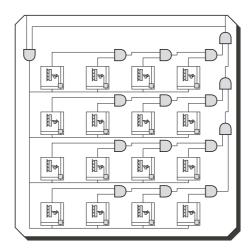

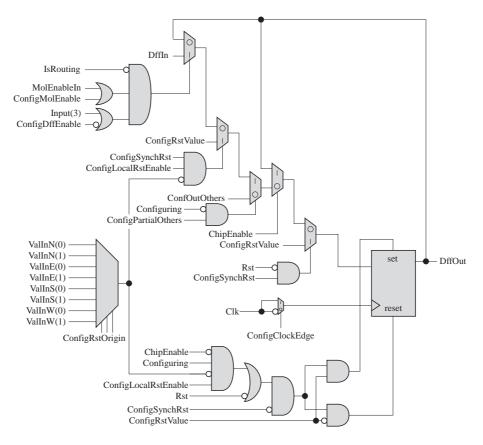

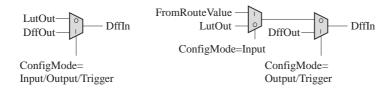

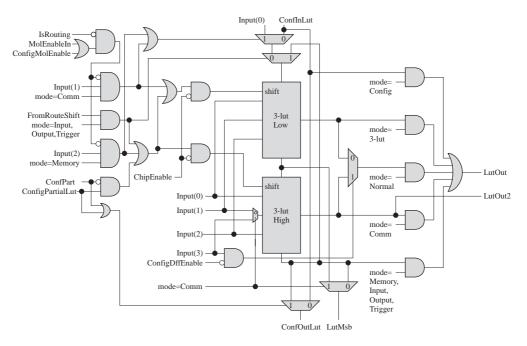

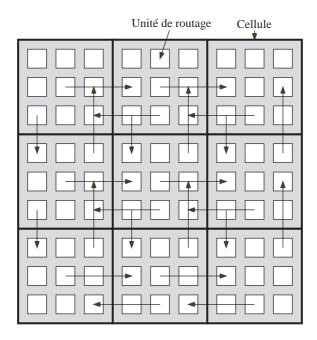

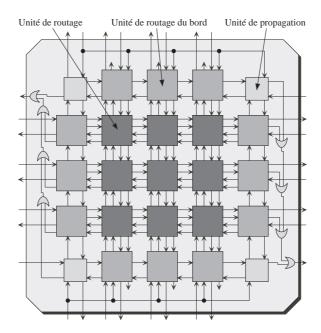

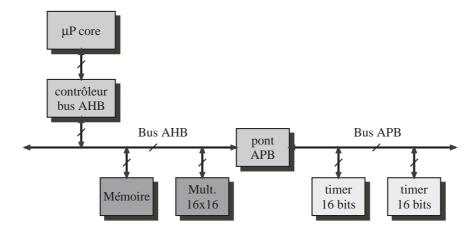

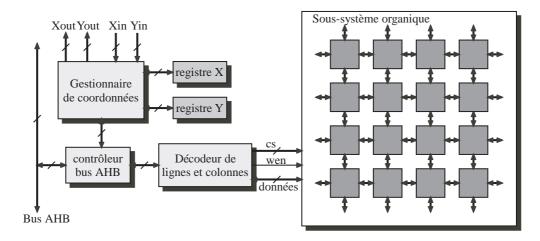

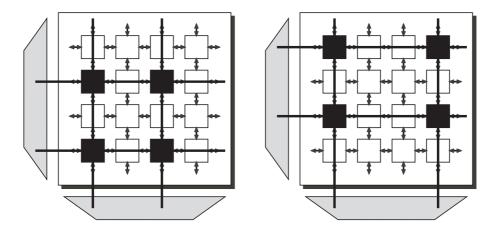

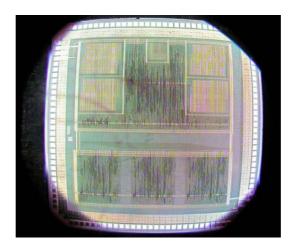

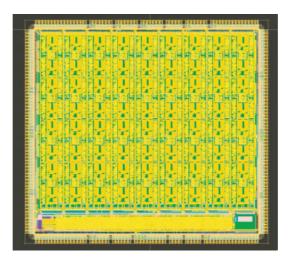

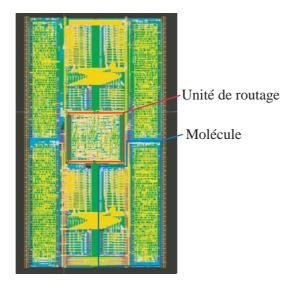

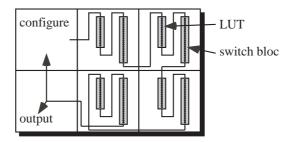

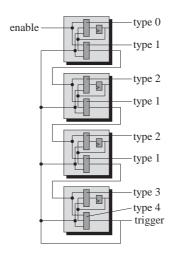

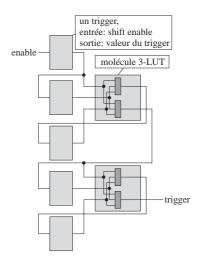

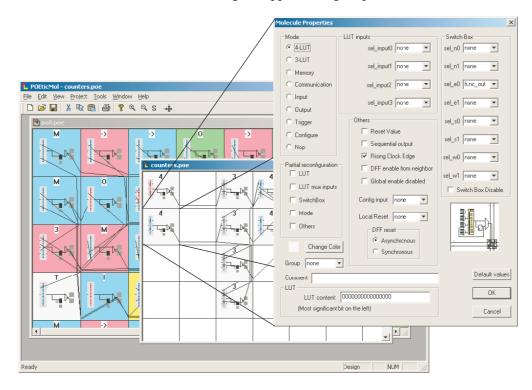

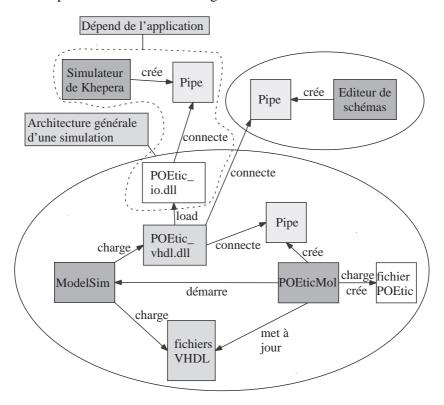

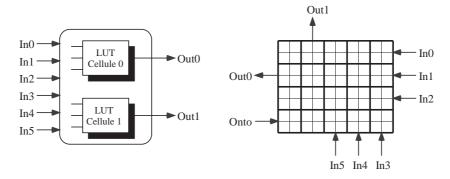

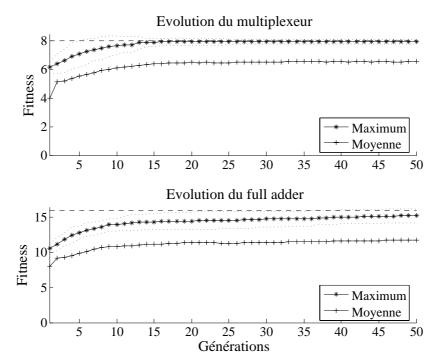

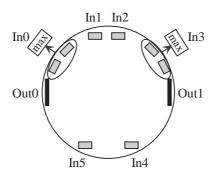

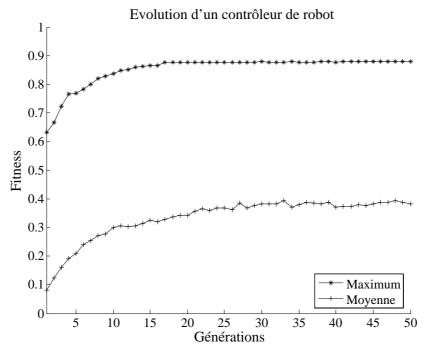

#### **PLA**